# Space Grade Parallel Persistent SRAM Memory

(AS301GB32, AS302GB32, AS304GB32, AS308GB32)

#### **Features**

- Interface

- Parallel Asynchronous x32

- Technology

- pMTJ STT-MRAM

- Virtually unlimited Endurance and Data Retention (see Table 17)

- Density

- 1Gb, 2Gb, 4Gb, 8Gb

- Memory Array Organization

- 1Gb : 33,554,432 x 32

- 2 Gb: 67,108,864 x 32

- 4 Gb : 134,217,728 x 32

- 8 Gb : 268,435,456 x 32

- Voltage Range

- Operating V<sub>CC</sub>: 2.50V 3.60V

- Vccio: 1.8V, 2.5V, 3.0V, 3.3V

- Under Radiation: V<sub>CC</sub>: 2.50V 3.00V \*

- V<sub>CCIO</sub>: 1.8V, 2.5V, 3.0V \*

- Temperature Range

- Operating -40°C to 125°C

- Operating under radiation -40°C to 85°C \*

- Packages

- 142-ball FBGA (15mm x 17mm)

- RoHS & REACH Compliant \*\*

- PEMS-INST-001 Flow \*\*\*

<sup>\*</sup> To assure a Safe Operating Area, limit the device to these specifications.

<sup>\*\*</sup> Leaded Balls available

<sup>\*\*\*</sup> PEMS-INST-001 Flow available as custom option through partners

#### **Table of Contents**

| Features                                 |    |

|------------------------------------------|----|

| General Description                      | 4  |

| Ordering Options                         | 5  |

| Valid Combinations — Standard            | 6  |

| Marking Specification — Standard         | 6  |

| Signal Description and Assignment        | 7  |

| Special Configuration Options            | 10 |

| ECC Registers                            | 10 |

| INT# functionality                       | 10 |

| Output Drive Strength Register           | 10 |

| Device Protection Register               | 11 |

| Package Options                          | 12 |

| 142-Ball FBGA – 1,2,4Gb                  | 12 |

| 142-Ball FBGA – 8Gb                      | 13 |

| 142-Ball FBGA Mechanical Drawing         | 14 |

| Normal Device Initialization:            | 17 |

| Electrical Specifications                | 19 |

| Write Operation                          | 23 |

| Bus Turnaround Operation – Read to Write | 25 |

| Read Operation                           | 26 |

| Asynchronous Page Mode                   | 27 |

| Asynchronous Page Mode Read Operation    | 28 |

| Asynchronous Page Mode Write Operation   | 29 |

| Asynchronous Page Mode AC Timing         | 30 |

| Endurance and Data Retention             | 30 |

| Thermal Resistance                       | 31 |

| Product Use Limitations                  | 32 |

| Limited Warranty                         | 32 |

| Revision History                         | 33 |

| Figure 1: Part Number Ordering Options                                            | 5  |

|-----------------------------------------------------------------------------------|----|

| Figure 2: Device Marking                                                          | 6  |

| Figure 3: Device Pinout                                                           | 7  |

| Figure 4: 142-ball FBGA                                                           | 13 |

| Figure 5: 142-ball FBGA Mechanical Drawing - 1,2,4 Gb                             | 14 |

| Figure 6: 142-ball FBGA Mechanical Drawing - 8 Gb                                 | 15 |

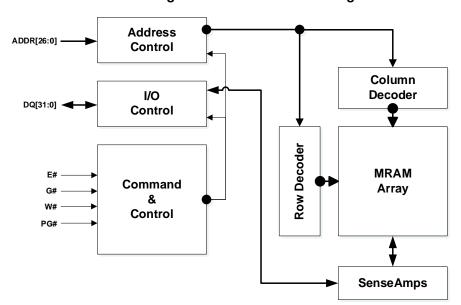

| Figure 7: Functional Block Diagram                                                | 16 |

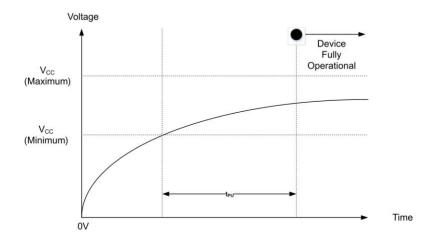

| Figure 8: Power-Up Behavior                                                       | 17 |

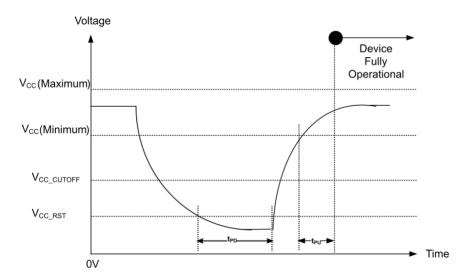

| Figure 9: Power-Down Behavior                                                     | 18 |

| Figure 10: Write Operation                                                        | 23 |

| Figure 11: Write Operation (E# Controlled)                                        | 24 |

| Figure 12: Bus Turnaround Operation                                               | 25 |

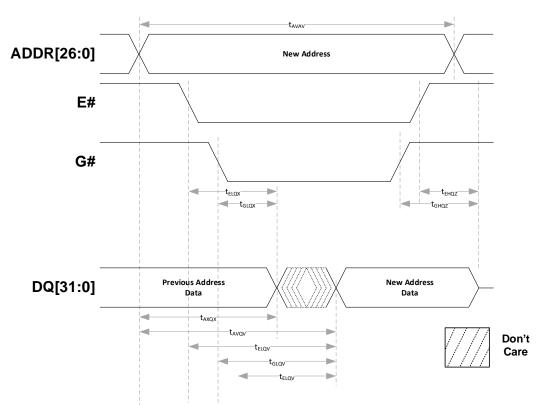

| Figure 13: Read Operation                                                         | 26 |

| Figure 14: 4-Word Asynchronous Page Mode Comparison with Legacy Asynchronous Mode | 27 |

| Figure 15: Page Mode Functional Block Diagram                                     | 28 |

| Figure 16: Asynchronous Page Read Operation                                       | 28 |

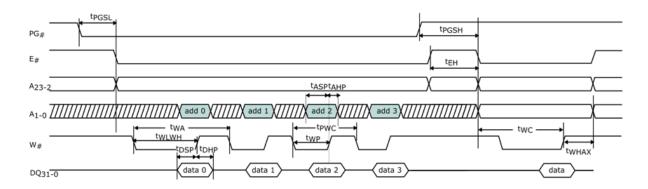

| Figure 17: Asynchronous Page Write Operation                                      | 29 |

| Figure 18: Page Write to Single Write Timing Diagram                              | 29 |

| Table 1: Technology Comparison                                                    | 4  |

| Table 2: Valid Combinations List                                                  | 6  |

| Table 3: Signal Description                                                       | 8  |

| Table 4: Power Up/Down Timing and Voltages                                        | 18 |

| Table 5: Device Initialization Timing and Voltages                                | 19 |

| Table 6: Recommended Operating Conditions                                         | 19 |

| Table 7: Pin Capacitance                                                          |    |

| Table 8: DC Characteristics                                                       | 20 |

| Table 9: Magnetic Immunity Characteristics                                        | 21 |

| Table 10: AC Test Conditions                                                      | 21 |

| Table 11: Absolute Maximum Ratings                                                | 22 |

| Table 12: Write Operation (W# Controlled)                                         | 23 |

| Table 13: Write Operation (E# Controlled)                                         | 24 |

| Table 14: Write Operation                                                         | 25 |

| Table 15: Read Operation                                                          | 26 |

| Table 16: Page Mode AC Timing                                                     | 30 |

| Table 17: Endurance and Data Retention                                            | 30 |

| Table 18: Thermal Resistance Specifications 142 Ball BGA                          | 31 |

# **General Description**

AS3xxx332 is a Spin-transfer torque Magneto-resistive random-access memory (STT-MRAM). It is offered in 1Gbit and 4Gbit. MRAM technology is analogous to Flash technology with SRAM compatible 45ns/45ns read/write timings (Persistent SRAM, P-SRAM). Data is always non-volatile. This makes MRAM a very reliable and fast non-volatile memory solution. Data is always non-volatile with 10<sup>16</sup> write cycles endurance and greater than 20-year retention @85°C.

Table 1: Technology Comparison

|                   | SRAM | Flash | EEPROM | MRAM     |

|-------------------|------|-------|--------|----------|

| Non-Volatility    | -    | V     | V      | V        |

| Write Performance | V    | _     | _      |          |

| Read Performance  |      | _     | _      | √        |

| Endurance         |      | _     | _      | <b>√</b> |

| Power             | _    | _     | _      | V        |

MRAM is a true random-access memory; allowing both reads and writes to occur randomly in memory. MRAM is ideal for applications that must store and retrieve data without incurring large latency penalties. It offers low latency, low power, high endurance, high performance and scalable memory technology.

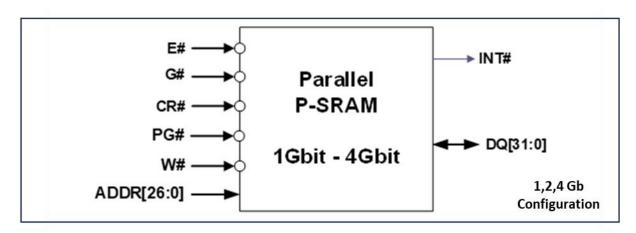

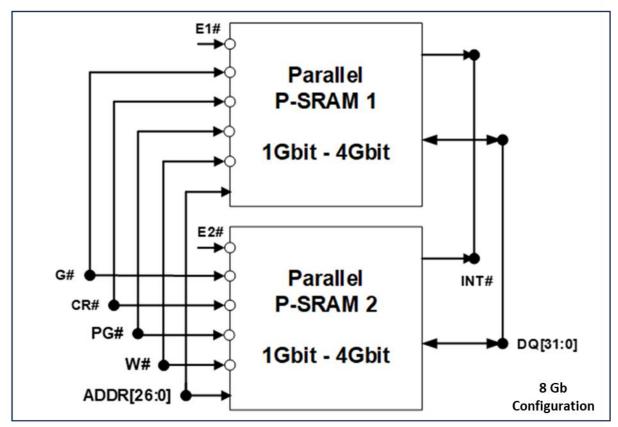

AS3xxx332 is available in small footprint (15mm x 17mm) 142 ball BGA package. In 1,2,4Gb densities the device uses one chip select E#. In this configuration one contigious address space of 1,2,4Gb is formed. In 8Gb configuration the package has two banks of 4 dies each selctable separately and not at the same time. Each bank is selectable using either E1# and E2#. In the 8Gb configuration E1# and E2# MUST NOT be selected simultaneously as the two banks share the same I/O pins.

AS3xxx332 is offered with industrial extended (-40°C to 125°C) operating temperature ranges: This is measured as the junction temperature.

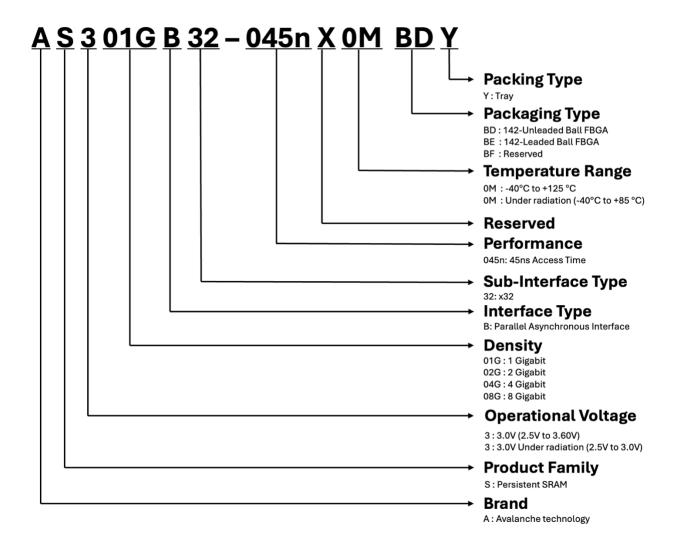

# **Ordering Options**

Revision: Y

The ordering part numbers are formed by a valid combination of the following options:

Figure 1: Part Number Ordering Options

#### Valid Combinations — Standard

Valid Combinations list includes device configurations currently available. Contact your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

Table 2: Valid Combinations List

| Valid Combinations – 45ns |                      |              |                 |                      |  |  |  |  |

|---------------------------|----------------------|--------------|-----------------|----------------------|--|--|--|--|

| Base Part Number          | Temperature<br>Range | Package Type | Packing<br>Type | Part<br>Number       |  |  |  |  |

| AS301GB32-045nX           | OM                   | BD           | Υ               | AS301GB32-045nX0MBDY |  |  |  |  |

| AS302GB32-045nX           | OM                   | BD           | Υ               | AS302GB32-045nX0MBDY |  |  |  |  |

| AS304GB32-045nX           | OM                   | BD           | Υ               | AS304GB32-045nX0MBDY |  |  |  |  |

| AS308GB32-045nX           | OM                   | BD           | Υ               | AS308GB32-045nX0MBDY |  |  |  |  |

| AS301GB32-045nX           | OM                   | BE           | Υ               | AS301GB32-045nX0MBEY |  |  |  |  |

| AS302GB32-045nX           | OM                   | BE           | Υ               | AS302GB32-045nX0MBEY |  |  |  |  |

| AS304GB32-045nX           | OM                   | BE           | Υ               | AS304GB32-045nX0MBEY |  |  |  |  |

| AS308GB32-045nX           | OM                   | BE           | Υ               | AS308GB32-045nX0MBEY |  |  |  |  |

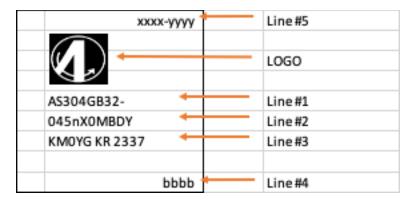

## Marking Specification — Standard

The device will be marked according to the following specification:

Line #1 & Line #2 will match the part number in Table 2

Line #3 Will show: 5 digit Alphanumeric Code + Country of Origin + Date Code

Line #4 May or May not be marked. This field is reserved for Avalanche Technology

Line #5 May or May not be marked. This field is reserved for Avalanche Technology

Figure 2: Device Marking

# **Signal Description and Assignment**

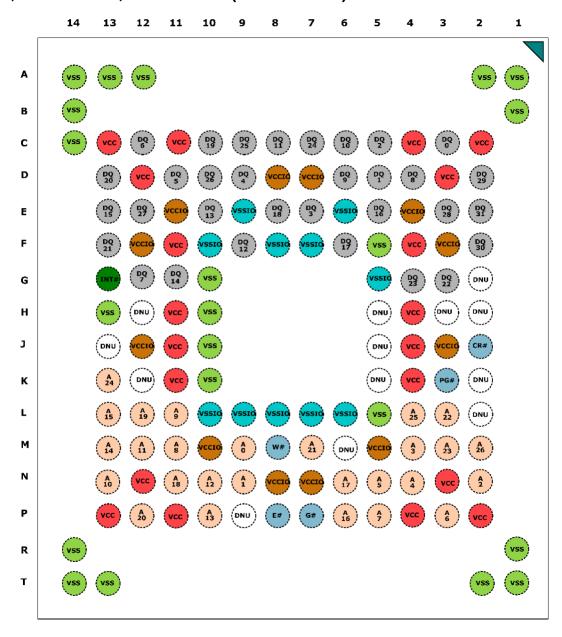

Figure 3: Device Pinout

Table 3: Signal Description

| Signal            | Ball<br>Assignment                                                                                                                                             | Туре           | Description                                                                                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E# / E1#          | P8                                                                                                                                                             | Input          | 1,2,4Gb (E#): Chip enable: Enables the MRAM array 8Gb (E1#): Chip enable: Enables the 1st bank of 4 MRAM die. There is an internal 10k Pullup. THIS SIGNAL MUST NOT BE ACTIVE AT THE SAME TIME AS E2#.     |

| DNU / E2#         | K5                                                                                                                                                             | DNU/Input      | 1,2,4Gb (DNU): It can be left floating and not connected.  8Gb (E2#): Chip enable: Enables the second bank of 4 MRAM die.  THIS SIGNAL MUST NOT BE ACTIVE AT THE SAME TIME AS E1#.                         |

| G#                | P7                                                                                                                                                             | Input          | Output enable: Enables the output drivers for data transfer I/Os.                                                                                                                                          |

| CR#               | J2                                                                                                                                                             | Input          | Configuration Register enable: Enables access to the Configuration registers                                                                                                                               |

| PG#               | K3                                                                                                                                                             | Input          | Page Mode: Enables Page mode access                                                                                                                                                                        |

| W#                | M8                                                                                                                                                             | Input          | <b>Write enable:</b> Transfers data from the host system to the MRAM when Low (Logic '0'). Transfers data from the MRAM to the host system when High (Logic '1').                                          |

| ADDR[26:0]        | M2, L4, K13,<br>M3, L3, M7,<br>P12, L12, N11,<br>N6, P6, L13,<br>M13, P10, N10,<br>M12, N13, L11,<br>M11, P5, P3,<br>N5, N4, M4, N2,<br>N9, M9                 | Input          | Address: I/Os for address transfer  1G: ADDR[24:0] – 25 Address pins for 1Gb x32 devices.*  2G: ADDR[25:0] – 26 Address pins for 2Gb x32 devices.**  4G: ADDR[26:0] – 27 Address pins for 4Gb x32 devices. |

| DQ[31:0]          | E2, F2, D2, E3,<br>E12, D10, C9,<br>C7, G4, G3,<br>F13, D13, C10,<br>E8, F6, E5, E13,<br>G11, E10, F9,<br>C8, C6, D6, D4,<br>G12, C12, D11,<br>D9, E7, C5, D5, | Input / Output | Data inputs/outputs: The bidirectional I/Os transfer data [31:0].                                                                                                                                          |

| INT# ***          | G13                                                                                                                                                            | Output         | <b>Interrupt:</b> Output generated by the MRAM when an unrecoverable ECC error is detected during read operation (output goes low on error): requires to have an external pull-up resistor $(4.7K\Omega)$  |

| Vccio             | F12, J12, E11,<br>M10, D8, N8,<br>D7, N7, M5, E4,<br>F3, J3                                                                                                    | Supply         | I/O power supply.                                                                                                                                                                                          |

| V <sub>ssio</sub> | F10, L10, E9,<br>L9, F8, L8, F7,<br>L7, E6, L6, G5,                                                                                                            | Supply         | I/O ground supply.                                                                                                                                                                                         |

| Vcc               | C13, P13, D12,<br>N12, C11, F11,<br>H11, J11, K11,<br>P11, C4, F4, H4,                                                                                         | Supply         | Core power supply.                                                                                                                                                                                         |

| Signal | Ball<br>Assignment                                                                                                | Туре   | Description                                |

|--------|-------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------|

|        | J4, K4, P4, D3,                                                                                                   |        |                                            |

|        | N3, C2, P2                                                                                                        |        |                                            |

| Vss    | A14, B14, C14,<br>H13, R14, T14,<br>A13, T13, A12,<br>G10, H10, J10,<br>K10, F5, L5, A2,<br>T2, A1, B1, R1,<br>T1 | Supply | Core ground supply.                        |

| DNU    | J13, H12, K12,<br>P9, M6, H5, J5,<br>H3, G2, H2, K2,<br>L2                                                        |        | Do Not Use: DNUs must be left unconnected. |

<sup>\*</sup> Unused ADDR[26:25] balls should be connected to Ground

<sup>\*\*</sup> Unused ADDR[25] balls should be connected to Ground

<sup>\*\*\*</sup> INT# is latched and must be reset/cleared by writing to the ECC Control register.

# **Special Configuration Options**

There are eight user accessible registers that control ECC, output drive strength and array write protection. All registers are 32-bit wide. These registers are only available during device configuration and not accessible to the user. In a multi-die configuration (2Gb, 4Gb) each 1Gb die has its own set of registers and need to be programmed individually. Each die needs to be selected using the upper 2 MSB address bits.

## **ECC Registers**

There are 6 registers that allow access to the ECC engine during the life of the product to access the functionality of the circuits. During normal use, the ECC engine will correct any soft errors.

## **INT#** functionality

As explained in the pinout, the INT# will go active if uncorrectable error is encountered. This is an open collector output which requires a pullup. In a multi-chip configuration (2G, 4G) the pin is shared between the dies. The recommended next steps are up to the system architect. The host must interrogate each die to identify which one/ones caused the interrupt to clear the INT Flag register.

#### ECC Control Register - Read and Write

| Bits   | Name              | Description                                                                                                      | Read /<br>Write | Default<br>State | Select Options                                            |

|--------|-------------------|------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------------------------------------------------|

| [31:2] | RSVD              | Reserved                                                                                                         | R               | 31'b0            | Reserved for future use                                   |

| [1]    | Interrupt Reset   | Resets the interrupt generated in response to detection of an unrecoverable error and clears the interrupt flag. | W               |                  | 0: Don't reset 1: Reset ECC unrecoverable error interrupt |

| [0]    | Error_Count_Reset | Resets the ECC<br>Error Count<br>Register                                                                        | W               | 0                | 0: Don't reset 1: Reset ECC Error Count Register to zero  |

## **Output Drive Strength Register**

The default setting of this register is 00.

Revision: Y

#### Output Drive Strength Register – Read and Write

| Bits   | Name                      | Description                                    | Read /<br>Write | Default<br>State | Selec | ct Option                                             | าร        |      |

|--------|---------------------------|------------------------------------------------|-----------------|------------------|-------|-------------------------------------------------------|-----------|------|

| [31:3] | RSVD                      | Reserved                                       | R               | 0                | Rese  | rved for                                              | future us | se   |

| [2]    | Enable_<br>Drive_Strength | Enables or disables the drive strength setting | R/W             | 0                | 1: Us | Default setting     Use output drive strength setting |           |      |

|        |                           |                                                |                 |                  |       | 1.8V                                                  | 2.5V      | 3.3V |

| [1:0]  | Output_Drive_             | Output drive                                   | R/W             | 00               | 00    | 1mA                                                   | 2.5mA     | 4mA  |

|        | Strength_Setting          | strength                                       |                 |                  | 01    | 3mA                                                   | 5mA       | 8mA  |

|        |                           |                                                |                 |                  | 10    | 5mA                                                   | 10mA      | 14mA |

|        |                           |                                                |                 |                  | 11    | 7mA                                                   | 14mA      | 18mA |

# **Device Protection Register**

It is possible to write protect the Memory array as shown in the table below. Note; The term full array is defined as an array of 1Gb.

#### Device Protection Register – Read and Write

| Bits   | Name       | Description                                | Read /<br>Write | Default<br>State | Select Options                                                                                                                                                                                                                 |

|--------|------------|--------------------------------------------|-----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:3] | RSVD       | Reserved                                   | R               | 29'b0            | Reserved for future use                                                                                                                                                                                                        |

| [2:0]  | BPSEL[2:0] | Enables or<br>disables block<br>protection | R/W             | 3'b0             | 000 – Disabled 001 – Protect upper 1/64 array 010 – Protect upper 1/32 array 011 – Protect upper 1/16 array 100 – Protect upper 1/8 array 101 – Protect upper 1/4 array 110 – Protect upper 1/2 array 111 – Protect full array |

# **Package Options**

142-Ball FBGA - 1,2,4Gb AS301GB32, AS302GB32, AS304GB32 (Bottom View)

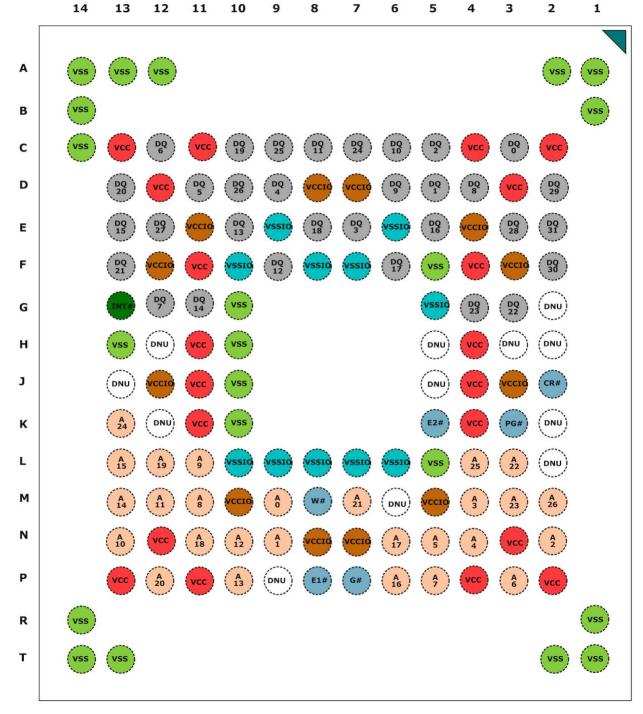

## 142-Ball FBGA – 8Gb AS308GB32 (Bottom View)

Figure 4: 142-ball FBGA

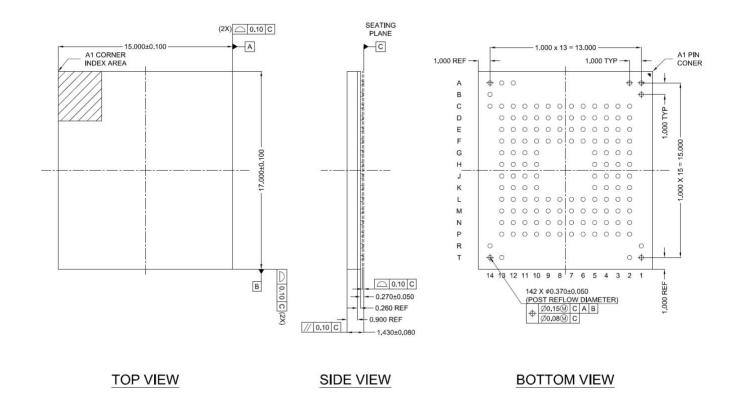

## 142-Ball FBGA Mechanical Drawing

Figure 5: 142-ball FBGA Mechanical Drawing - 1,2,4 Gb

#### [NOTES]

#### 1. SOLDER BALL SIZE IS

0.35 mm before reflow

0.37 (+/-0.05) mm post reflow

2. SOLDER RESIST OPENING IS

0.300 mm

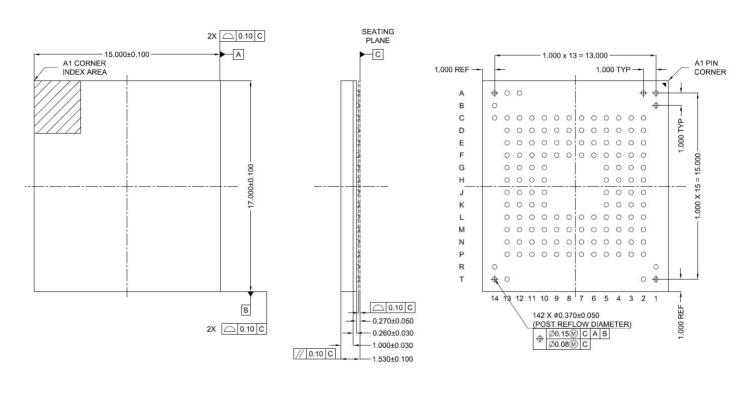

Figure 6: 142-ball FBGA Mechanical Drawing - 8 Gb

TOP VIEW SIDE VIEW BOTTOM VIEW

#### [NOTES]

- 1. SOLDER BALL SIZE IS

- 0.35 mm before reflow

- 0.37 (+/-0.05) mm post reflow

- 2. SOLDER RESIST OPENING IS

- 0.300 mm

## **Architecture**

AS3xxx332 is a high performance MRAM device. Writing to and reading from the device are performed as follows:

To write to the device, drive Chip Enable (E#) and Write Enable (W#) inputs Low (Logic '0'). This enables data on I/O pins (DQ[0] to DQ[31]) to be written into the memory location specified by the address pins (ADDR[0] through ADDR[26]).

To read from the device, drive Chip Enable (E#) input Low (Logic '0'), Output Enable (G#) input Low (Logic '0') while maintaining Write Enable (W#) High (Logic '1'). This enables data from the memory location specified by the address pins (ADDR[0] through ADDR[26]) to appear on I/O pins (DQ[0] to DQ[31]).

In the case of the 8Gb device: This architecture is duplicated. Each bank of 4 dies is controlled with a separate chipselect: E1#, E2#.

Figure 7: Functional Block Diagram

Table 4: Modes of Operation

| Mode            | E# | G# | W# | Current         | DQ[31:0] |

|-----------------|----|----|----|-----------------|----------|

| Not Selected    | Н  | Х  | Х  | I <sub>SB</sub> | Hi-Z     |

| Output Disabled | L  | Н  | Н  | IREAD           | Hi-Z     |

| Read Word       | L  | L  | Н  | IREAD           | Data-out |

| Write Word      | L  | X  | L  | IWRITE          | Data-in  |

#### Notes:

H: High (Logic '1') X: Don't Care L: Low (Logic '0') Hi-Z: High Impedance

## **Normal Device Initialization:**

When powering up, the following procedure is required to initialize the device correctly:

- V<sub>CC</sub> and V<sub>CCIO</sub> can ramp up together (R<sub>VR</sub>), if not possible then V<sub>CC</sub> first followed by V<sub>CCIO</sub>. The maximum difference between the two voltages should not exceed 0.7V before reaching the final value of Vccio.

- The device must not be selected at power-up (a  $10K\Omega$  pull-up Resistor to  $V_{CCIO}$  on E# is recommended). Then a further delay of tpu (Figure 8) until Vcc reaches Vcc(minimum).

- During Power-up, recovering from power loss or brownout, a delay of tpu is required before normal operation commences (Figure 6).

Figure 8: Power-Up Behavior

When powering down, the following procedure is required to turn off the device correctly:

- V<sub>CC</sub> and V<sub>CCIO</sub> can ramp down together (R<sub>VF</sub>), if not possible then V<sub>CC</sub> first followed by VCCIO. The maximum difference between the two voltages should not exceed 0.7V.

- The device must not be selected at power-down (a 10KΩ pull-up Resistor to V<sub>CCIO</sub> on E# is recommended).

- It is recommended that no instructions are sent to the device when V<sub>CC</sub> is below V<sub>CC</sub> (minimum).

- During power loss or brownout, when V<sub>CC</sub> goes below V<sub>CC-CUTOFF</sub>. The voltage must drop below  $V_{CC}$ (Reset) for a period of tpp. The power-up timing needs to be observed after  $V_{CC}$  goes above V<sub>CC</sub>(minimum)

Figure 9: Power-Down Behavior

Table 4: Power Up/Down Timing and Voltages

| Parameter                                       | Symbol                 | Test Conditions                         | Minimum | Typical | Maximum | Units |

|-------------------------------------------------|------------------------|-----------------------------------------|---------|---------|---------|-------|

| Vcc Range                                       |                        | All operating voltages and temperatures | 2.7     | -       | 3.6     | V     |

| Vcc Ramp Up Time                                | R <sub>VR</sub>        |                                         | 30      | -       | -       | μs/V  |

| V <sub>CC</sub> Ramp Down Time                  | R <sub>VF</sub>        |                                         | 20      | -       | -       | μs/V  |

| V <sub>CC</sub> Power Up to First Instruction   | tpu                    |                                         | 1       | -       | -       | ms    |

| Vcc (low) time                                  | tpD                    |                                         | 1       |         |         | ms    |

| V <sub>CC</sub> Cutoff - Must Initialize Device | V <sub>CC_CUTOFF</sub> |                                         | 1.6     | -       | -       | V     |

| V <sub>CC</sub> (Reset)                         | Vcc_rst                |                                         | 0       |         | 0.3     | V     |

Table 5: Device Initialization Timing and Voltages

| Parameter                                     | Symbol          | Test Conditions        | Minimum | Typical | Maximum | Units |

|-----------------------------------------------|-----------------|------------------------|---------|---------|---------|-------|

| V <sub>CC</sub> Range                         |                 |                        | 2.5     | -       | 3.6     | V     |

| V <sub>CC</sub> Ramp Up Time                  | RvR             | All operating voltages | 30      | -       | -       | µs/V  |

| V <sub>CC</sub> Ramp Down Time                | R <sub>VF</sub> | and temperatures       | 20      | -       | -       | μs/V  |

| V <sub>CC</sub> Power Up to First Instruction | tpu             |                        | 250     | -       | -       | μs    |

| Vcc Cutoff - Must Initialize Device           | Vcc-cutoff      |                        | 1.6     | -       | -       | V     |

# **Electrical Specifications**

**Table 6: Recommended Operating Conditions**

|                     | Parameter / Condition                   | Minimum | Typical   | Maximum | Units |

|---------------------|-----------------------------------------|---------|-----------|---------|-------|

|                     | Operating Temperature (T <sub>A</sub> ) | -40.0   | -         | 125.0   | °C    |

| Normal<br>Operation | Vcc Supply Voltage                      | 2.5     | 3.0       | 3.6     | V     |

| Operation           | V <sub>CCIO</sub> Supply Voltage        | 1.71    | 1.8 - 3.0 | 3.6     | V     |

|                     | Operating Temperature (T <sub>A</sub> ) | -40.0   | -         | 85.0    | °C    |

| Under<br>Radiation  | Vcc Supply Voltage                      | 2.5     | 2.7       | 3.0     | V     |

| Radiation           | Vccio Supply Voltage                    | 1.71    | 1.8 - 3.0 | 3.0     | V     |

|                     | V <sub>SS</sub> Supply Voltage          | 0.0     | 0.0       | 0.0     | V     |

|                     | V <sub>SSIO</sub> Supply Voltage        | 0.0     | 0.0       | 0.0     | V     |

|                     | Vwi Write Inhibit Voltage               | 2.1     | 2.3       | 2.5     | V     |

Table 7: Pin Capacitance

| Parameter                      | Symbol | Test Conditions                                    | Density | Maximum | Units |

|--------------------------------|--------|----------------------------------------------------|---------|---------|-------|

| Input Pin Capacitance          |        |                                                    | 1Gb     | 10.0    |       |

|                                | Cin    | TEMP = $25^{\circ}$ C; f = 1 MHz;<br>$V_{IN} = 0V$ | 2/4Gb   | 20.0    |       |

|                                |        |                                                    | 8Gb     | 40.0    |       |

|                                |        |                                                    | 1Gb     | 10.0    | pF    |

| Input / Output Pin Capacitance | CINOUT | TEMP = 25°C; f = 1 MHz;<br>V <sub>IN</sub> = 0V    | 2/4Gb   | 20.0    |       |

|                                |        |                                                    | 8Gb     | 40.0    |       |

Table 8: DC Characteristics

|                                                   |                 |                                             |         | 3.             | 0V Device             | e (2.5V-3.6    | V)               |       |

|---------------------------------------------------|-----------------|---------------------------------------------|---------|----------------|-----------------------|----------------|------------------|-------|

| Parameter                                         | Symbol          | Test Conditions                             | Density | Min            | Typic al <sup>1</sup> | 85° <b>C</b> ² | Max <sup>3</sup> | Units |

|                                                   |                 |                                             | 1Gb     |                | 25                    | 50             | 80               |       |

|                                                   |                 | V <sub>CC</sub> (max),                      | 2Gb     |                | 50                    | 100            | 150              | 1     |

| Read Current                                      | IREAD IOUT=0mA  | 4Gb                                         |         | 70             | 200                   | 300            | -                |       |

|                                                   |                 |                                             | 8Gb     |                | 140                   | 400            | 600              |       |

|                                                   |                 |                                             | 1Gb     |                | 20                    | 50             | 80               |       |

|                                                   |                 |                                             | 2Gb     |                | 50                    | 100            | 150              | mA    |

| Write Current                                     | IWRITE          | Vcc (max)                                   | 4Gb     |                | 65                    | 200            | 300              |       |

|                                                   |                 |                                             | 8Gb     |                | 130                   | 400            | 600              | 1     |

|                                                   |                 | E#=V <sub>IH</sub> ,<br>Vcc (max)           | 1Gb     |                | 25                    | 50             | 75               | -     |

| Standby Current                                   | I <sub>SB</sub> |                                             | 2Gb     |                | 45                    | 100            | 140              |       |

| (-40°C to 125°C)                                  |                 |                                             | 4Gb     |                | 60                    | 180            | 280              |       |

|                                                   |                 |                                             | 8Gb     |                | 120                   | 360            | 560              |       |

| Input Leakage Current                             | lu              | V <sub>IN</sub> =0 to V <sub>CC</sub> (max) |         | -              | -                     |                | ±1.0             | μA    |

| Output Leakage Current                            | ILO             | Vout=0 to Vcc (max)                         |         | -              | -                     |                | ±1.0             | μA    |

| Input High Voltage (V <sub>CCIO</sub> =1.71-2.2)  |                 |                                             |         | 0.65*<br>Vccio | -                     |                | Vccio<br>+0.2    |       |

| Input High Voltage (Vccio=2.2-2.7)                | Vıн             |                                             |         | 1.8            |                       |                |                  | V     |

| Input High Voltage (Vccio=2.7-3.6)                | -               |                                             |         | 2.2            |                       |                |                  |       |

| Input Low Voltage (V <sub>CCIO</sub> =1.71-2.2)   |                 |                                             |         |                | -                     |                | 0.35*            |       |

| Input Low Voltage (Vccio=2.2-2.7)                 | VIL             |                                             |         | -0.2           |                       |                | 0.7              | V     |

| Input Low Voltage (Vccio=2.7-3.6)                 | -               |                                             |         |                |                       |                | 0.8              | -     |

| Output Low Voltage (Vccio=1.71-2.2)               |                 | $I_{OL} = 0.1 \text{mA}$                    |         |                |                       |                | 0.0              |       |

| Output Low Voltage (Vccio=2.2-2.7)                | V <sub>OL</sub> | I <sub>OL</sub> = 0.1mA                     |         | _              |                       |                | 0.4              | V     |

| Output Low Voltage (Vccio=2.7-3.6)                | -               | I <sub>OL</sub> = 2.0mA                     |         |                |                       |                | 0.4              | 1     |

| Output High Voltage (V <sub>CCIO</sub> =1.71-2.2) |                 | I <sub>OH</sub> = -0.1mA                    |         | 1.4            |                       |                |                  |       |

| Output High Voltage (Vccio=2.2-2.7)               | Voн             | I <sub>OH</sub> = -0.1mA                    |         | 2.0            |                       |                | _                | V     |

| Output High Voltage (Vccio=2.7-3.6)               | -               | I <sub>OH</sub> = -1.0mA                    |         | 2.4            |                       |                |                  |       |

Notes:

<sup>&</sup>lt;sup>1</sup> Typical values are measured at 25°C

<sup>&</sup>lt;sup>2</sup> 85°C values are guaranteed by characterization; not tested in production

<sup>&</sup>lt;sup>3</sup> Max values are measured at 125°C

## Table 9: Magnetic Immunity Characteristics

| Parameter                   | Symbol                 | Maximum | Units |

|-----------------------------|------------------------|---------|-------|

| Magnetic Field During Write | H <sub>max_write</sub> | 24000   | A/m   |

| Magnetic Field During Read  | H <sub>max_read</sub>  | 24000   | A/m   |

#### Table 10: AC Test Conditions

| Parameter                                  | Value                   |

|--------------------------------------------|-------------------------|

| Input pulse levels                         | 0.0V to V <sub>CC</sub> |

| Input rise and fall times                  | 5ns                     |

| Input and output measurement timing levels | Vcc/2                   |

| Output Load                                | CL = 30pF               |

# Absolute Maximum Ratings

Stresses greater than those listed may cause permanent damage to the device. This is a stress rating only. Exposure to maximum rating for extended periods may adversely affect reliability.

Table 11: Absolute Maximum Ratings

| Parameter                                                     | Minimum | Maximum     | Units |

|---------------------------------------------------------------|---------|-------------|-------|

| Magnetic Field During Write                                   |         | 24000       | A/m   |

| Magnetic Field During Read                                    |         | 24000       | A/m   |

| Temperature Under Bias                                        | -45     | 130         | °C    |

| Storage Temperature                                           | -55 to  | 150         | °C    |

| Supply Voltage Vcc                                            | -0.5    | 4.0         | V     |

| I/O Voltage Vccio                                             | -0.5    | 3.8         | V     |

| Voltage on any pin except Vcc                                 | -0.5    | Vccio + 0.2 | V     |

| ESD HBM (Human Body Model)<br>ANSI/ESDA/JEDEC JS-001-2017     | ≥  200  | 00 V        | V     |

| ESD CDM (Charged Device Model)<br>ANSI/ESDA/JEDEC JS-002-2018 | ≥  50   | 0 V         | V     |

| Latch-Up (I-test)<br>JESD78                                   | ≥  100  | mA          | mA    |

| Latch-Up (Vsupply over-voltage test) JESD78                   | Pas     | sed         |       |

# **Write Operation**

ADDR[26:0] **New Address** E# t<sub>wLwH</sub> W# DQ[31:0] **New Address** Data Don't Care

Figure 10: Write Operation

Table 12: Write Operation (W# Controlled)

| Parameter                               | Symbol            | Minimum | Maximum | Units |

|-----------------------------------------|-------------------|---------|---------|-------|

| Write Cycle Time                        | t <sub>AVAV</sub> | 45      | -       | ns    |

| Address Set-Up Time                     | t <sub>AVWL</sub> | 0       | -       | ns    |

| Address Valid to end of Write (G# High) | t <sub>AVWH</sub> | 28      | -       | ns    |

| Address Valid to end of Write (G# Low)  | t <sub>AVWH</sub> | 30      | -       | ns    |

| Write Pulse Width (G# High)             | twlwh, twleh      | 25      | -       | ns    |

| Write Pulse Width (G# Low)              | twlwh, twleh      | 25      | -       | ns    |

| Data Valid to end of Write              | t <sub>DVWH</sub> | 15      | -       | ns    |

| Data Hold Time                          | t <sub>WHDX</sub> | 0       | -       | ns    |

| Write recovery Time                     | twhax             | 12      | -       | ns    |

#### Notes:

G# is High (Logic '1') for Write operation

Power supplies must be stable

Addresses valid either before or at the same time as E# goes low

-t<sub>avav</sub> ADDR[26:0] **New Address** -t<sub>ELWH</sub> W# t<sub>AVEH</sub> E# DQ[31:0] New Address Data Don't Care

Figure 11: Write Operation (E# Controlled)

Table 13: Write Operation (E# Controlled)

| Parameter                               | Symbol                                | Minimum | Maximum | Units |

|-----------------------------------------|---------------------------------------|---------|---------|-------|

| Write Cycle Time                        | t <sub>AVAV</sub>                     | 45      | -       | ns    |

| Address Set-Up Time                     | t <sub>AVEL</sub>                     | 0       | -       | ns    |

| Address Valid to end of Write (G# High) | t <sub>AVEH</sub>                     | 28      | -       | ns    |

| Address Valid to end of Write (G# Low)  | t <sub>AVEH</sub>                     | 30      | -       | ns    |

| Write Pulse Width (G# High)             | t <sub>ELWH</sub> , t <sub>ELEH</sub> | 25      | -       | ns    |

| Write Pulse Width (G# Low)              | t <sub>ELWH</sub> , t <sub>ELEH</sub> | 25      | -       | ns    |

| Data Valid to end of Write              | t <sub>DVEH</sub>                     | 15      | -       | ns    |

| Data Hold Time                          | t <sub>EHDX</sub>                     | 0       | -       | ns    |

| Write recovery Time                     | t <sub>EHAX</sub>                     | 12      | -       | ns    |

#### Notes:

G# is High (Logic '1') for Write operation Power supplies must be stable

Addresses valid either before or at the same time as W# goes low

# **Bus Turnaround Operation – Read to Write**

ADDR[26:0] **New Address** E# W# **DQ[31:0]** - Datain Data **DQ[31:0] -** Dataout Don't Care

Figure 12: Bus Turnaround Operation

Table 14: Write Operation

| Parameter                | Symbol | Minimum | Maximum | Units |

|--------------------------|--------|---------|---------|-------|

| W# Low to Data Hi-Z      | twlqz  | 0       | 15      | ns    |

| W# High to Output Active | twhqx  | 3       | -       | ns    |

#### Notes:

Power supplies must be stable

Addresses valid either before or at the same time as E# goes low

# **Read Operation**

Figure 13: Read Operation

Table 15: Read Operation

| Parameter                          | Symbol            | Minimum | Maximum | Units |

|------------------------------------|-------------------|---------|---------|-------|

| Read Cycle Time                    | t <sub>AVAV</sub> | 45      | -       | ns    |

| Address Cycle Time                 | t <sub>AVQV</sub> | -       | 45      | ns    |

| Chip Enable Access Time            | t <sub>ELQV</sub> | -       | 45      | ns    |

| Output Enable Access Time          | t <sub>GLQV</sub> | -       | 25      | ns    |

| Output Hold From Address Change    | t <sub>AXQX</sub> | 3       | -       | ns    |

| Chip Enable Low to Output Active   | t <sub>ELQX</sub> | 3       | -       | ns    |

| Output Enable Low to Output Active | t <sub>GLQX</sub> | 0       | -       | ns    |

| Chip Enable High to Output Hi-Z    | t <sub>EHQZ</sub> | 0       | 15      | ns    |

| Output Enable High to Output Hi-Z  | tghqz             | 0       | 15      | ns    |

Notes:

W# is High (Logic '1') for Read operation

Power supplies must be stable

Addresses valid either before or at the same time as E# goes low

# **Asynchronous Page Mode**

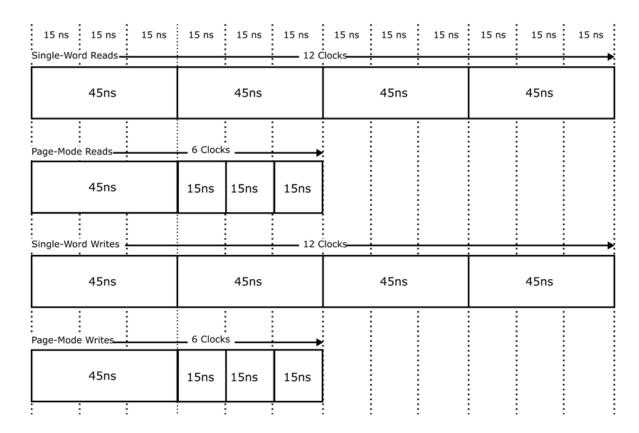

Asynchronous page mode is an extension of the legacy asynchronous read and write operations that improves the performance of the MRAM memory, as shown in Figure 11. On power up or reset, the MRAM memory defaults to legacy asynchronous mode to enable controllers to immediately access the memory. Page mode is also immediately available after asserting PG# low and E# high. No special commands or setup are necessary.

Figure 14: 4-Word Asynchronous Page Mode Comparison with Legacy Asynchronous Mode

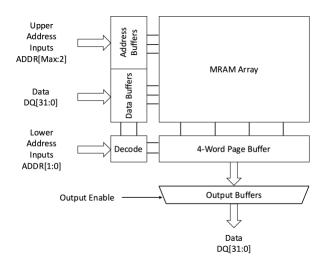

Figure 12 shows the page mode functional block diagram. During a page write, a new page is accessed by changing any of the upper addresses A[max:2]. A subsequent write commands (W# toggle) can load the data buffers with new data to be written to any of the adjacent addresses A[1:0]. During page read, an initial asynchronous read access if executed during which 4 data words are read from the memory array simultaneously, and loaded into an internal page buffer, while the first data word is output onto the memory bus. Subsequent reads are output from the data buffer, providing up to two times the read and write access speed of conventional asynchronous reads.

Figure 15: Page Mode Functional Block Diagram

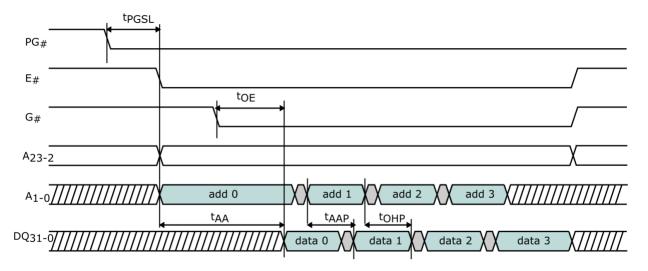

# **Asynchronous Page Mode Read Operation**

Asynchronous page mode reads are initiated by the memory controller in the same way as asynchronous single-word reads by asserting E# or changing any of the upper addresses A[max:2]. In Figure 13; an address is placed on the address bus, and E# and G# are asserted. Multiple data words are "sensed" simultaneously, and loaded into an internal page buffer while the first data word is being output onto the data bus. After the initial-access delay (tAA), read data is driven onto the data bus and then sampled by the memory controller. When the next read address is within the page-buffer range A[1:0], subsequent data is output from the page buffer, not from the MRAM array. A shorter access delay (tAAP) occurs when data is read from the page buffer. The low-order address bits are used to access the page buffer, and determine which word is output. Four-word page access uses A[1:0];

Figure 16: Asynchronous Page Read Operation

#### Notes:

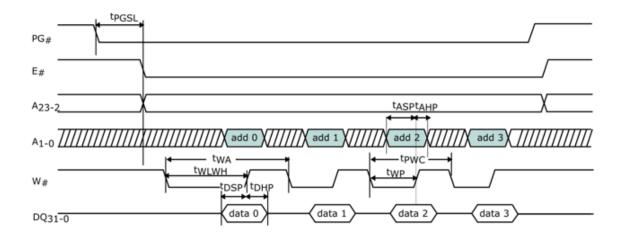

# **Asynchronous Page Mode Write Operation**

For Asynchronous page mode write, shown in Figure 14, the first write pulse defines the first write access (t<sub>PWC</sub>). While E# is maintained LOW, a subsequent write pulse along with a new adjacent address A[1:0] executes a page mode write access. E# must be LOW upon completion of a page write access. Asserting E# HIGH at the beginning or the middle of a page access will abort it.

Figure 17: Asynchronous Page Write Operation

#### Notes:

In case of the 8G device: E# is represented by E1# or E2#

# **Asynchronous Page Mode Write to Single Write**

On power up or reset, the MRAM memory defaults to the legacy asynchronous mode. The page mode is immediately available after asserting PG# low while maintaining E# HIGH for tPGSL. Returning to legacy mode can be achieved by asserting PG# HIGH and E# for tpgsh.

Figure 18: Page Write to Single Write Timing Diagram

# **Asynchronous Page Mode AC Timing**

Table 16: Page Mode AC Timing

| Parameters        | Description                               | Min | Max | Unit |

|-------------------|-------------------------------------------|-----|-----|------|

| t <sub>WA</sub>   | Write access time                         | 45  | -   | ns   |

| t <sub>WC</sub>   | Chip enable LOW to write enable HIGH      | 30  | -   | ns   |

| t <sub>WHAX</sub> | Write recovery time                       | 15  | -   | ns   |

| t <sub>WLWH</sub> | Write enable low time                     | 25  | -   | ns   |

| t <sub>AS</sub>   | Address setup time (to E# Low)            | 0   | -   | ns   |

| t <sub>E</sub>    | Chip enable access time                   | -   | 45  | ns   |

| t <sub>AA</sub>   | Address access time                       | -   | 45  | ns   |

| to                | Output enable access time                 | =   | 15  | ns   |

| t <sub>PWC</sub>  | Page mode write access                    | 15  |     | ns   |

| t <sub>WP</sub>   | Page mode write enable low time           | 7.5 |     | ns   |

| t <sub>WPH</sub>  | Page mode write enable high time          | 7.5 |     | ns   |

| t <sub>AHP</sub>  | Page mode address hold time (to W# High)  | 6   |     | ns   |

| t <sub>ASP</sub>  | Page mode address setup time (to W# High) | 7.5 |     | ns   |

| t <sub>AAP</sub>  | Page mode address access time             | =   | 15  | ns   |

| t <sub>OHP</sub>  | Page mode output hold time                | 5   | -   | ns   |

| t <sub>PGSL</sub> | Page mode select to E# Low                | 10  | -   | ns   |

| t <sub>PGSH</sub> | Page mode unselect to E# Low              | 10  | -   | ns   |

| t <sub>PGH</sub>  | Page mode high time                       | 45  | -   | ns   |

| t <sub>EH</sub>   | E# High time                              | 10  | -   | ns   |

| t <sub>OH</sub>   | Output hold time                          | 5   | -   | ns   |

| t <sub>EP</sub>   | Page mode E# low time                     | 45  | -   | ns   |

| t <sub>DSP</sub>  | Page mode data setup time (to W# High)    | 7.5 | -   | ns   |

| t <sub>DHP</sub>  | Page mode data hold time (to W# High)     | 6   | -   | ns   |

# **Endurance and Data Retention**

Table 17: Endurance and Data Retention

| Parameter       | Symbol | Test Conditions | Minimum          | Units  |

|-----------------|--------|-----------------|------------------|--------|

| Write Endurance | END    | -               | 10 <sup>16</sup> | cycles |

| Data Retention  |        | 125°C           | 10               |        |

|                 |        | 105°C           | 10               |        |

|                 | RET    | 85°C            | 1,000            | years  |

|                 |        | 75°C            | 10,000           |        |

|                 |        | 65°C            | 1,000,000        |        |

# **Thermal Resistance**

Table 18: Thermal Resistance Specifications 142 Ball BGA

| Parameter | Description                              | Test Condition                                                                                                                   | 1Gb   | 2Gb | 4Gb   | 8Gb | Units  |

|-----------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-----|--------|

| θја       | Thermal resistance (junction to ambient) | Test conditions<br>follow standard<br>test methods and<br>procedures for<br>measuring<br>thermal<br>impedance, per<br>EIA/JESD51 | 17.89 | TBD | 17.90 | TBD | - °C/W |

| θις       | Thermal resistance (junction to case)    |                                                                                                                                  | 2.10  | TBD | 2.19  | TBD |        |

#### Notes:

- 1: These parameters are guaranteed by characterization; not tested in production.

- 2: Ambient temperature, T<sub>A</sub> 25 °C

- 3: Worst case Junction temp specified for Top die  $(\theta_{JA})$  and Bottom die  $(\theta_{JC})$

## **Product Use Limitations**

Avalanche reserves the right to make changes to the information in this document, and related hardware, software and system (collectively referred to as "**Products**") without notice. This document supersedes and replaces any and all prior or contemporaneous information or arrangement of any kind relating to the subject matter hereof. This document and any information set forth herein may not be reproduced without the prior written permission from Avalanche.

<u>Critical Applications</u>. Products are not authorized for use in applications in which failure of the Avalanche component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("**Critical Applications**"). Avalanche assumes no liability for Products if used for Critical Applications. Should customer or distributor purchase, use, or sell any Avalanche component for Critical Applications, customer and distributor shall indemnify and hold harmless Avalanche and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such Critical Application, whether or not Avalanche or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Products.

<u>Automotive Applications</u>. Products are not authorized for use in automotive applications unless specified by Avalanche. Avalanche assumes no liability for Products if used for automotive applications. Distributor and customer shall assume the sole risk and liability for such use and shall indemnify and hold Avalanche harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of Products in automotive applications.

<u>Customer Responsibility</u>. Customers are solely responsible for the design and operation of their systems using Products. It is customer's sole responsibility to determine whether Products are suited for their system. Customers are required to incorporate good safety design measures and adequate safeguards to eliminate risks of personal injury, death, or severe property or environmental damages that could result from failure of Products. **AVALANCHE ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS AND DAMAGES OR LOSSES OCCURING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.**

The information contained herein is presented only as guidance for Product use. Avalanche assumes no responsibility for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Products. No license to any intellectual property right is granted by this document, whether expressed or implied. You may not perform compositional, structural, functional or other analysis of Products, or undertake deconvolution or reverse engineering with respect to Products.

#### **Limited Warranty**

In no event shall Avalanche and its representatives be liable for any indirect, incidental, punitive, special or consequential damages (including but not limited to loss of use, revenue or profit), whether or not such damages are based on tort, warranty, breach of contract or other legal theory.

In no event shall Avalanche's aggregate liability for any breach, warranty, indemnity or other obligation or liability arising out of or in connection with the sale of Products or the use of any Products exceed the purchase price of the particular Product(s) or services with respect to which losses or damages are claimed.

# **Revision History**

| Revision | Date       | Change Summary                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| REV A    | 11/19/2019 | Preliminary release                                                                                                                                                                                                                                                                                                                                                                                           |  |

| REV B    | 12/19/19   | Removed commercial grade Added x32 configuration Removed 54-pin TSOP Added 92-ball FBGA Updated DC characteristics and pin capacitance Updated part number options                                                                                                                                                                                                                                            |  |

| REV C    | 02/19/2020 | Added 125 degrees option Updated 92-ball package                                                                                                                                                                                                                                                                                                                                                              |  |

| REV D    | 10/8/2020  | Removed 256Mb density and added 2Gb density Removed Industrial, Industrial Extended temp grade options, added military temp grade option Removed 35ns performance option Updated 92-FBGA dimensions Added radiation specs Updated OPN decoder and valid combinations Updated Electrical Specifications, write operation specifications and read operation specifications. Added Endurance and Retention specs |  |

| REV E    | 10/23/2020 | Removed radiation specs                                                                                                                                                                                                                                                                                                                                                                                       |  |

| REV F    | 3/15/2021  | Added 4Gb device option Changed 92-ball BGA to 142-ball BGA; updated package ball assignments and outline drawing Added Asynchronous Page Mode Removed Industrial and Industrial Plus temp grades Removed sleep mode                                                                                                                                                                                          |  |

| REV G    | 5/27/2021  | Updated BGA Pin assignments                                                                                                                                                                                                                                                                                                                                                                                   |  |

| REV H    | 6/15/2021  | Corrected INT# pin assignment and updated package drawings                                                                                                                                                                                                                                                                                                                                                    |  |

| REV I    | 6/15/2021  | Remove restrictions of use in Military applications Changed temp spec to -40. Plastic parts will only be qualified to -40 degrees Centigrade.                                                                                                                                                                                                                                                                 |  |

| REV J    | 6/21/2021  | Updated Package Ball assignment to conform to JEDED standard                                                                                                                                                                                                                                                                                                                                                  |  |

| REV K    | 8/23/2021  | Updated Page mode timing: Tpwc in table 15. Corrected Isb in summary table Added Pin descriptions for E# and PG#. Updated timing diagrams (Figures 15, 16 & 17) to show E# instead of CE#; W# instead of WE# and G# instead of OE#. Removed Byte enable from Table 14                                                                                                                                         |  |

| REV L    | 9/3/2021   | Updated package dimension to show Ball diameter Removed redundant notes describing dimensions on package dimension page. Fixed I/O Power legend to show VCCQ                                                                                                                                                                                                                                                  |  |

| REV M    | 9/29/2021  | Removed 512Mb and 2Gb densities Removed Tape & Reel as an ordering option Added Vccio to the specification                                                                                                                                                                                                                                                                                                    |  |

| REV N    | 10/20/2021 | Added 64 and 256Mb densities Added Hardware RST# pin Temp spec in Part number corrected to show 0M                                                                                                                                                                                                                                                                                                            |  |

| REV O    | 12/09/2021 | Added V <sub>DD</sub> and V <sub>BYP</sub> pin description and PowerUp/Powerdown sequence                                                                                                                                                                                                                                                                                                                     |  |

| REV S    | 12/20/2021 | Updated Table 5 with Vcc Ramp time                                                                                                                                                                                                                                                                                                                                                                            |  |

| REV T  | 01/18/2022 | Removed 64 and 256Mb densities from this data sheet                                                                                 |  |

|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| REV U  | 03/31/2022 | Renamed VCCQ to VCCIO                                                                                                               |  |

|        |            | Added pin assignment table                                                                                                          |  |

|        |            | Relaxed Vdd spec to +-7.5% from +-5%                                                                                                |  |

| U.1    | 04/29/2022 | Added ball assignment of ADDR[17:12] to signal description table                                                                    |  |

|        |            | Added package thermal                                                                                                               |  |

| U.2    | 05/16/2022 | Updated Pictures with new Figure #                                                                                                  |  |

|        |            | Updated DC Characteristics Table: Current numbers are based on UMC's                                                                |  |

|        |            | analysis of their current 22nm process.                                                                                             |  |

|        | 05/00/0000 | Added V <sub>DD</sub> to supply line on Front page                                                                                  |  |

| U.3    | 05/23/2022 | Updated Power sequencing description under DEVICE INITIALIZATION                                                                    |  |

|        |            | Added Absolute Maximum Ratings Table                                                                                                |  |

| 11.4   | 05/05/0000 | Called out specific voltages are allowed for V <sub>CCIO</sub> on front page.                                                       |  |

| U.4    | 05/25/2022 | Removed Power sequencing case of VDD going low before VCC                                                                           |  |

| DEVV   | 07/04/2022 | Added Absolute Maximum rating on V <sub>DD</sub>                                                                                    |  |

| REV V  | 07/01/2022 | Changed the nominal height to be compatible with Gen 3 Serial devices: Nominal Thickness in Figure 4 changed from 1.39mm to 1.43mm. |  |

|        |            |                                                                                                                                     |  |

| REV W  | 07/19/2022 | Leaded ball options added to Order Option Table  Removed Performance table                                                          |  |

| KEV VV | 01/19/2022 | Added Extended Safe Operating Area as well as Normal Operating Conditions                                                           |  |

|        |            | Removed redundant Package drawing table                                                                                             |  |

|        |            | Fixed wording on use of V <sub>BYP</sub> in pin definition table                                                                    |  |

| REV X  | 12/15/2022 | Ball K3 (previously designated as #PG) is re-assigned as Reserved and                                                               |  |

|        |            | must be pulled high to Vccio through a 10kΩ resistor (This is the fast page                                                         |  |

|        |            | function. For compatibility with SRAM devices, this function is now                                                                 |  |

|        |            | reserved and only available for custom designs).                                                                                    |  |

|        |            | This device is now available for use in LEO. The Extended Safe Operating                                                            |  |

|        |            | Area (ESOA) is no longer described here and is only available through our                                                           |  |

|        |            | partner program: As such Ball K12 (previously external Vdd) is now NC                                                               |  |

|        |            | and H13 (previously V <sub>BYP</sub> ) has to be connected to Vss.                                                                  |  |

|        |            | Added 85°C power consumption to DC Characteristics Table 8.                                                                         |  |

| X.1    | 03/28/2023 | Nominal Thikcness in Figure 4 changed from 1.43mm to 1.51mm.                                                                        |  |

| X.2    | 04/10/2023 | Added 4.7KΩ pull up to INT#                                                                                                         |  |

|        |            | Added Asynchronous Page Mode Read & Write: This functionality has                                                                   |  |

|        |            | always been in the silicon. It is now fully tested and verified effective with                                                      |  |

| V 0    | 05/04/0000 | date code: 2250 for 1Gb devices and 2240 for 4Gb devices.                                                                           |  |

| X.3    | 05/01/2023 | Voltage Ramp Up rate has been clarified in the Normal Device                                                                        |  |

|        |            | Initialization.                                                                                                                     |  |

|        |            | Input & Output Low & High Voltage levels have been redefined as                                                                     |  |

| X.4    | 05/08/2023 | references to V <sub>CCIO</sub> rather than V <sub>CC</sub> in the DC Characteristics Table 8.                                      |  |

| 7.4    | 03/00/2023 | Page Mode write Timing was updated to match the read timing. Lead cycle is the same 45ns for Read and Write.                        |  |

|        |            | Specified Max temp to be junction rather than ambiet                                                                                |  |

| X.5    | 07/20/2023 | K12 was mislabelled in Figure 3 as "NC". It is "DNU" Corrected the picture.                                                         |  |

| X.6    | 08/31/2023 | Added 2Gb density                                                                                                                   |  |

| 7•     | 00/01/2020 | Updated Input & Output Low and High Voltage levels DC Charaterstics                                                                 |  |

|        |            | table 8 to be consistent at 1.8V operation                                                                                          |  |

|        |            | Clarification that PEMS-INST-001 flow version of product will be supplied                                                           |  |

|        |            | through a partner                                                                                                                   |  |

|        |            | Table 3: Signal desciption: Corrected definition of W# and removed RFU.                                                             |  |

|        |            | Table 11: Corrected signal name: Changed V <sub>DD</sub> to V <sub>CC</sub>                                                         |  |

|        |            | Guideline on normal device initialization corrected to say: pullup on E# is to                                                      |  |

|        |            | Vccio                                                                                                                               |  |

| X.7    | 10/17/2023 | Fixed Typo in Signal pin description Table 3 DQ[31:0]                                                                               |  |

|        |            | Added Special Configuration Registers                                                                                               |  |

|       |            | Added 8Gb density                                                                                 |

|-------|------------|---------------------------------------------------------------------------------------------------|

|       |            | Updated Maximum rating table 11                                                                   |

|       | 12/13/2023 | Updated Solder ball and Solder resist opening dimensions on the Package drawing                   |

|       | 01/04/2024 | Updated Table 16 Page Mode AC Timing signal name/descriptions                                     |

|       |            | Package naming convention: Ball assignement pictures used to say:                                 |

|       |            | Top View. The label should have read: Bottom View                                                 |

|       | 01/18/2024 | Added Mechanical drawing for 8Gb                                                                  |

| X.8   | 03/26/2024 | Corrected Modes Of Operation Table "Removed Output Disabled mode with E#, G#, W# set to L, X, X". |

|       |            | Removed DC output Current lout from Absolute Maximum Ratings Table:                               |

|       |            | Correct Maximum Current should be taken from the DC Charcterstics table                           |

|       |            | base don number of dies in the device.                                                            |

|       |            | INT# definition was updated: When triggered this signal remains low and                           |

|       |            | must be cleared by writing to the ECC Control register.                                           |

| REV Y | 03/28/2024 | Added Safe Operating Area Specification: Extended the Operational                                 |

|       | 04/05/2024 | voltage to 2.5V as a minimum.                                                                     |

|       |            | Added Marking Specification.                                                                      |

|       | 04/09/2024 | Corrected 8Gb Ball Map to be consistent with the 1/2/4Gb Ball Map.                                |