# AS3xxGB32 Reference Design Utilizing Lattice MachX03 FPGA Platform Application Note

AN000018 provides basis functional operation of the Avalanche AS3xxGB32 P-SRAM Parallel x32 devices and several key P-SRAM board design considerations.

# 1. Introduction

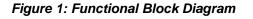

The AS3xxGB32 is a high-speed asynchronous SRAM with densities offered in 1Gb and 4Gb, organizing in 32K bytes x 32 bits and 128K bytes x 32 bits respectively. The scalarly advanced 22nm STT-MRAM technology coupled with innovative circuit design provide low latency, high performance, and very reliable non-volatile memory solution. The Avalanche's 3rd Generation P-SRAM is ideal for Defense and Aerospace applications.

Memory access is controlled by Chip Enable (E#), Output Enable (G#) and Write Enable (W#).

To write to the device, drive Chip Enable (E#) and Write Enable (W#) inputs Low (Logic '0'). This enables data on I/O pins (DQ[0] to DQ[31]) to be written into the memory location specified by the address pins (ADDR[0] through ADDR[24]).

To read from the device, drive Chip Enable (E#) input Low (Logic '0'), Output Enable (G#) input Low (Logic '0') while maintaining Write Enable (W#) High (Logic '1'). This enables data from the memory location specified by the address pins (ADDR[0] through ADDR[24]) to appear on I/O pins (DQ[0] to DQ[31]).

## **Signal Description**

### Table 1: Signal Description

| Signal            | Ball<br>Assignment                                                                                                                                                   | Туре           | Description                                                                                                                                                              |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| E#                | P8                                                                                                                                                                   | Input          | Chip enable: Enables or disables the MRAM.                                                                                                                               |  |  |

| G#                | P7                                                                                                                                                                   | Input          | Output enable: Enables the output drivers for data transfer I/Os.                                                                                                        |  |  |

| CR#               | J2                                                                                                                                                                   | Input          | <b>Configuration Register enable:</b> Enables access to the Configuration registers                                                                                      |  |  |

| W#                | M8                                                                                                                                                                   | Input          | Write enable: Transfers serial data from the host system to the MRAM when Low (Logic '0'). Transfers serial data from the MRAM to the host system when High (Logic '1'). |  |  |

| ADDR[26:0]        | M2, L4, K13,<br>M3, L3, M7,<br>P12, L12, N11,<br>N6, P6, L13,<br>M13, P10, N10,<br>M12, N13, L11,<br>M11, P5, P3,<br>N5, N4, M4, N2,<br>N9, M9                       | Input          | Address: I/Os for address transfer<br>1G: ADDR[24:0] – 25 Address pins for 1Gb x32 devices.*<br>4G: ADDR[26:0] – 27 Address pins for 4Gb x32 devices.                    |  |  |

| DQ[31:0]          | E2, F2, D2, E3,<br>E12, D10, C9,<br>C7, G4, G3,<br>F13, D13, C10,<br>E8, F6, E5, E13,<br>G11, E10, F9,<br>C8, C6, D6, D4,<br>G12, C12, D11,<br>D9, E7, C5, D5,<br>C3 | Input / Output | Data inputs/outputs: The bidirectional I/Os transfer data [15:0].                                                                                                        |  |  |

| INT#              | G13                                                                                                                                                                  | Output         | <b>Interrupt:</b> Output generated by the MRAM when an unrecoverable ECC error is detected during read operation (output goes low on error).                             |  |  |

| V <sub>CCIO</sub> | F12, J12, E11,<br>M10, D8, N8,<br>D7, N7, M5, E4,<br>F3, J3                                                                                                          | Supply         | I/O power supply.                                                                                                                                                        |  |  |

| V <sub>SSIO</sub> | F10, L10, E9,<br>L9, F8, L8, F7,<br>L7, E6, L6, G5,                                                                                                                  | Supply         | I/O ground supply.                                                                                                                                                       |  |  |

| V <sub>cc</sub>   | C13, P13, D12,<br>N12, C11, F11,<br>H11, J11, K11,<br>P11, C4, F4, H4,<br>J4, K4, P4, D3,<br>N3, C2, P2                                                              | Supply         | Core power supply.                                                                                                                                                       |  |  |

| V <sub>ss</sub>   | A14, B14, C14,<br>H13, R14, T14,<br>A13, T13, A12,<br>G10, H10, J10,                                                                                                 | Supply         | Core ground supply.                                                                                                                                                      |  |  |

| Signal | Ball<br>Assignment                                             | Туре | Description                                                                                   |

|--------|----------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------|

|        | K10, F5, L5, A2,<br>T2, A1, B1, R1,<br>T1                      |      |                                                                                               |

| DNU    | J13, H12, K12,<br>P9, M6, H5, J5,<br>K5, H3, G2, H2,<br>K2, L2 |      | Do Not Use: DNUs must be left unconnected.                                                    |

| RFU    | КЗ                                                             |      | <b>Reserved for Future Use:</b> requires to have an external pull-up resistor (10K $\Omega$ ) |

\* Unused ADDR[26:25] balls should be connected to Ground

# 2. Functional Feature

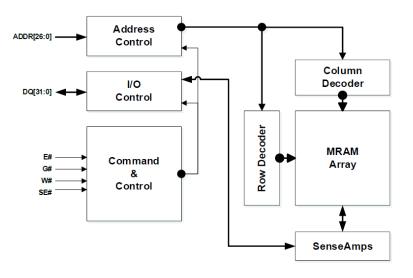

### 2.1 Write & Read Timing

### 2.1.1 Write Operation

#### Table 2: Write Operation

| Parameter                               | Symbol            | Minimum | Maximum | Units |

|-----------------------------------------|-------------------|---------|---------|-------|

| Write Cycle Time                        | tavav             | 45      | -       | ns    |

| Address Set-Up Time                     | <b>t</b> avwl     | 0       | -       | ns    |

| Address Valid to end of Write (G# High) | tavwн             | 28      | -       | ns    |

| Address Valid to end of Write (G# Low)  | tavwн             | 30      | -       | ns    |

| Write Pulse Width (G# High)             | twlwh, twleh      | 25      | -       | ns    |

| Write Pulse Width (G# Low)              | twlwh, twleh      | 25      | -       | ns    |

| Data Valid to end of Write              | tovwн             | 15      | -       | ns    |

| Data Hold Time                          | t <sub>WHDX</sub> | 0       | -       | ns    |

| Write recovery Time                     | t <sub>WHAX</sub> | 12      | -       | ns    |

#### Notes:

G# is High (Logic '1') for Write operation Power supplies must be stable

Addresses valid either before or at the same time as E# goes low

### 2.1.2 Read Operation

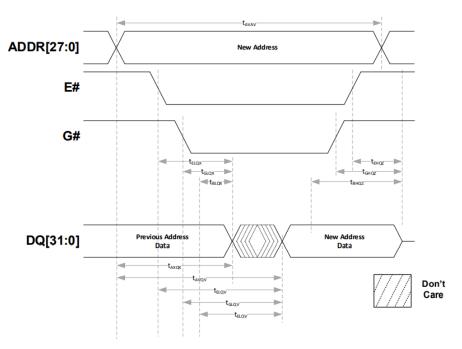

#### Figure 3: Read Timing

#### Table 3: Read Operation

| Parameter                          | Symbol            | Minimum | Maximum | Units |

|------------------------------------|-------------------|---------|---------|-------|

| Read Cycle Time                    | tavav             | 45      | -       | ns    |

| Address Cycle Time                 | <b>t</b> AVQV     | -       | 45      | ns    |

| Chip Enable Access Time            | <b>t</b> ELQV     | -       | 45      | ns    |

| Output Enable Access Time          | <b>t</b> GLQV     | -       | 25      | ns    |

| Byte Enable Access Time            | t <sub>BLQV</sub> | -       | 25      | ns    |

| Output Hold From Address Change    | taxox             | 3       | -       | ns    |

| Chip Enable Low to Output Active   | t <sub>ELQX</sub> | 3       | -       | ns    |

| Output Enable Low to Output Active | <b>t</b> GLQX     | 0       | -       | ns    |

| Byte Enable Low to Output Active   | t <sub>BLQX</sub> | 0       | -       | ns    |

| Chip Enable High to Output Hi-Z    | <b>t</b> EHQZ     | 0       | 15      | ns    |

| Output Enable High to Output Hi-Z  | <b>t</b> GHQZ     | 0       | 15      | ns    |

| Byte Enable High to Output Hi-Z    | t <sub>BHQZ</sub> | 0       | 10      | ns    |

Notes:

W# is High (Logic '1') for Read operation

Addresses valid either before or at the same time as E# goes low

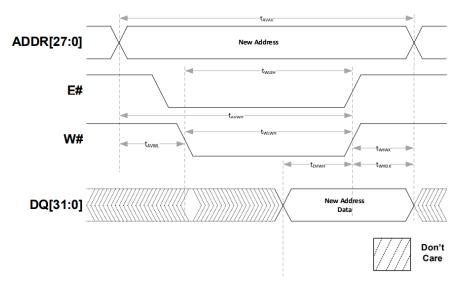

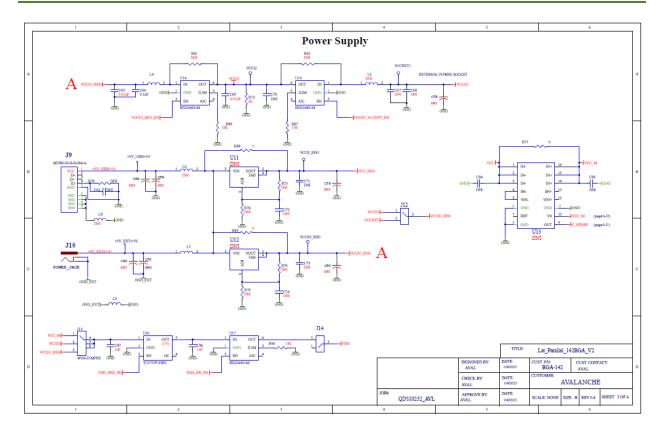

### 2.3 P-SRAM Power Up and Power Down Consideration

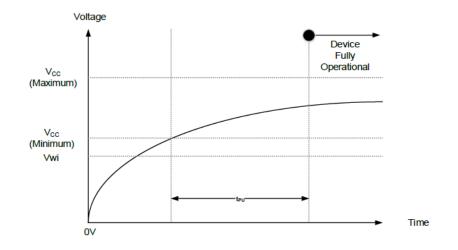

When powering up, the following procedure is required to initialize the device correctly:

- Vcc and Vccio can ramp up together (RvR), if not possible then Vcc first followed by Vccio. The maximum difference between the two voltages should not exceed 0.7V.

- The device must not be selected at power-up (E# must follow the applied voltage on V<sub>CC</sub> (a 10KΩ pull-up Resistor to V<sub>CC</sub> is recommended)) until V<sub>CC</sub> reaches V<sub>CC</sub>(minimum) and then a further delay of t<sub>PU</sub> (Figure 8).

- During Power-up, recovering from power loss or brownout, a delay of t<sub>PU</sub> is required before normal operation commences (Figure 4).

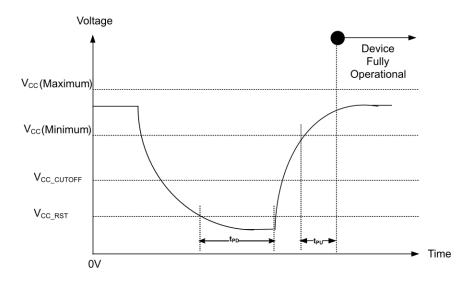

When powering down, the following procedure is required to turn off the device correctly:

- Vcc and Vccio can ramp down together (RvF), if not possible then Vcc first followed by VCCIO. The maximum difference between the two voltages should not exceed 0.7V.

- The device must not be selected at power-down (E# must follow V<sub>CC</sub> during power-down (a 10KΩ pull-up Resistor to V<sub>CC</sub> is recommended)) until V<sub>CC</sub> reaches VSS.

- It is recommended that no instructions are sent to the device when V<sub>CC</sub> is below V<sub>CC</sub> (minimum).

- During power loss or brownout, when V<sub>CC</sub> goes below V<sub>CC-CUTOFF</sub>. The voltage must drop below V<sub>CC</sub>(Reset) for a period of tPD. The power-up timing needs to be observed after V<sub>CC</sub> goes above V<sub>CC</sub>(minimum)

Power supplies must be stable

Figure 4: Power Up Behavior

#### Figure 5: Power Down Behavior

Table 4: Device Initialization Timing

| Parameter                                     | Symbol | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------------------------------|--------|-----------------|---------|---------|---------|-------|

| V <sub>cc</sub> Range                         |        | All operating   | 2.7     | -       | 3.6     | V     |

| V <sub>cc</sub> Ramp Up Time                  | Rvr    | voltages and    | 30      | -       | -       | µs/V  |

| V <sub>cc</sub> Ramp Down Time                | Rvf    | temperatures    | 20      | -       | -       | µs/V  |

| V <sub>cc</sub> Power Up to First Instruction | tPU    |                 | 1       | -       | -       | ms    |

| Parameter                                       | Symbol          | Test Conditions | Minimum | Typical | Maximum | Units |

|-------------------------------------------------|-----------------|-----------------|---------|---------|---------|-------|

| V <sub>cc</sub> (low) time                      | t <sub>PD</sub> |                 | 1       |         |         | ms    |

| V <sub>CC</sub> Cutoff – Must Initialize Device | Vcc_cutoff      |                 | 1.6     | -       | -       | V     |

| V <sub>cc</sub> (Reset)                         | Vcc_rst         |                 | 0       |         | 0.3     | V     |

# 3. P-SRAM Parallel System Design Consideration

## 3.1 PCB Layout Guideline

### 3.1.1 Power and Ground Planes

Power planes improve decoupling between circuits, preventing noise from propagating through the power supply from one circuit to another. In addition, they enable larger current carrying capacity, lowering the operating temperature of the board.

Ground planes in multi-layer board simplifies connecting each component to the ground net, provides clear return path on the ground plane and reduces noise and interference.

• The test board is designed with 8-layers, including 2 power planes and 2 ground planes.  $50\Omega \pm 10\%$ , 8mil traces are used to reduce the trace impedance.

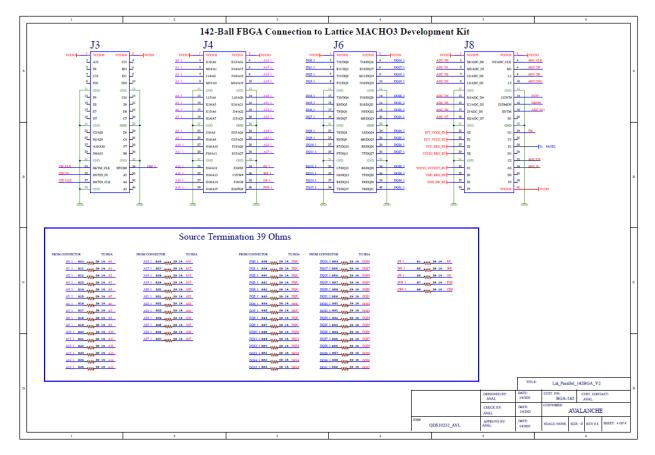

### 3.1.2 Reflection, Terminations and CrossTalk

Figure 6: Termination Resistor

|                        | Source re              | rmination 39 Ohms         |                           |                              |

|------------------------|------------------------|---------------------------|---------------------------|------------------------------|

| FROM CONNECTOR TO BGA  | FROM CONNECTOR TO BGA  | FROM CONNECTOR TO BGA     | FROM CONNECTOR TO BGA     |                              |

| A0 1 810_WW 39 1% A0   | A16 1 R26 WW 39 1% A16 | DQ0 1 #38 39 14 DQ0       | DQ16 1 #54 39 1% DQ16     | E# 1 R1_WW-39 1% E#          |

| Al   R11_WW-39 1% Al   | A17 1 827 WW 39 18 A17 | DQ1 1 #39 AWA 39 18 DQ1   | DQ17 1 855 WW 39 18 DQ17  | W# 1 R5 39 18 W#             |

| A2 1 812 WW 39 18 A2   | A18 1 R28 WW 39 1% A18 | DQ2 1 840 AWA 39 18 DQ2   | DQ18 1 856 WWW 39 18 DQ18 | G# 1 R6 39 18 G#             |

| A3 1 813 WW 39 18 A3   | A19 1 R29 WW 39 1% A19 | DQ3 1 841 WW 39 18 DQ3    | DQ19 1 857 39 18 DQ19     | PG# 1 R7 WW 39 18 PG#        |

| A4 1 814 WW 39 18 A4   | A20 1 830 WW 39 1% A20 | DQ4 1 842 WW 39 18 DQ4    | DQ20 1 858 WWW 39 1% DQ20 | CR# 1 R8 WW 39 18 CR#        |

| A5 1 815 WW 39 18 A5   | A21 1 831 WW 39 18 A21 | DQ5 1 843 WW 39 18 DQ5    | DQ21 1 859 WWW 39 18 DQ21 |                              |

| A6 1 816 WW 39 18 A6   | A22 1 R32 WW 39 1% A22 | DO6 1 R44 AMA 39 18 DO6   | DQ22 1 860 AWW 39 18 DQ22 |                              |

| A7 1 817 WW 39 18 A7   | A23 1 R33 WW 39 18 A23 | DQ7 1 845 WW 39 18 DQ7    | DQ23 1 861 39 1% DQ23     |                              |

| AS   R18 WW 39 1% AS   | A24 1 R34 WW 39 18 A24 | DOS 1 846 AMA 39 18 DOS   | D024 1 862 WWW 39 1% D024 |                              |

| A9 ] R19 WW 39 18 A9   | A25 1 R35 WW 39 1% A25 | DQ9 1 847 WW 39 18 DQ9    | DQ25 1 R63 WWW 39 1% DQ25 | MDS 0 R86_WW-39 1% GND       |

| A10 1 820 WW 39 18 A10 | A26 1 R36 WW 39 1% A26 | DQ10   R48 WW 39 18 DQ10  | DQ26 1 R64 39 1% DQ26     | MDS 1 R87_WW-39 1% GND       |

| All 1 821_WW 39 1% All | A27 1 R37 WW 39 1% A27 | DOI1 1 849 WW 39 18 DOI1  | DQ27 1 R65_WW_39 1% DQ27  | mds an pad R88_WW-39 1% (GND |

| A12 1 #22 39 1% A12    |                        | DQ12 1 850 WW 39 18 DQ12  | DQ28 1 86639 1% DQ28      |                              |

| A13 1 823 WW 39 18 A13 |                        | DQ13 1 851 WW 39 14 DQ13  | DQ29 1 867 WW 39 1% DQ29  |                              |

| Al4 1 824 WW 39 18 Al4 |                        | DQ14 1 R52 WW 39 14 DQ14  | DQ30 1 868 WW 39 1% DQ30  |                              |

| A15 1 825 WW 39 18 A15 |                        | DQ15 1 R53 AMA 39 18 DQ15 | DQ31 1 R69 WWW 39 16 DQ31 |                              |

- Clock signal is kept 3-4 times (24-25mil) away from other signals to avoid crosstalk.

- 39 Ohm resistor is used on each address, data and control signal

### 3.1.3 Signal Length Matching

• Address signal group, data signal group, control signal group and clock are within 10ps. Clock signal is kept about 25mil away from other signals to ensure signal integrity.

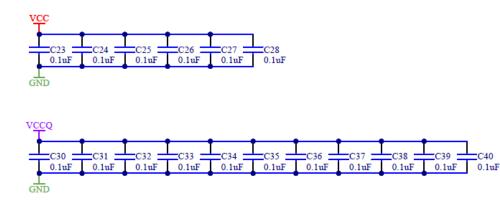

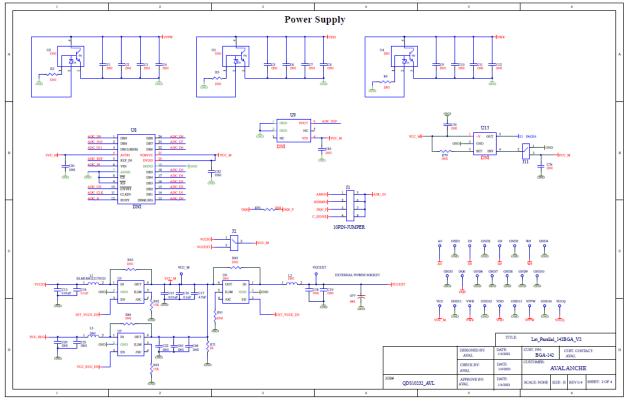

# 3.2 Decoupling/Bypass Capacitor

Selecting the right decoupling capacitor is important in the P-SRAM parallel design. It provides a low impedance path from the power plane to the ground plan and further prevent voltage swing on the power and ground pins. The recommendations are as follows:

- Keep decoupling capacitors as close to the component as possible

- For each active component, additional capacitors are required (refer to schematic below)

- Keep capacitors on the same side of the AS3xxGB32 if possible

- On V<sub>CC</sub> and V<sub>CCQ</sub>, multiple 0.1µF capacitors are required (refer to figure 7)

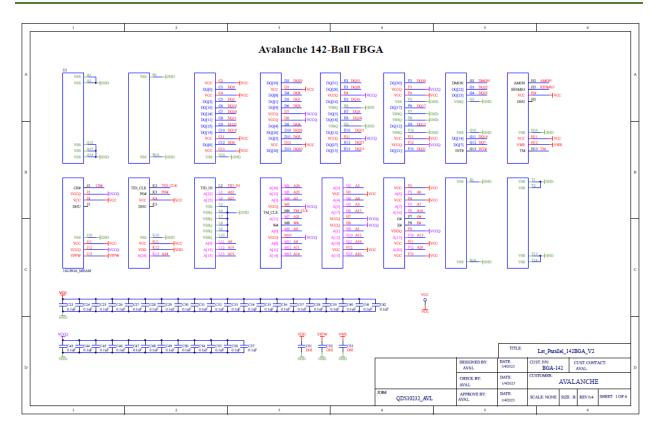

#### Figure 7: Decoupling Capacitor

### 3.3 Reference Schematic

### AN000018

• BOMs, Board Layout, Gerber File and IBIS/Verilog models are available per request.

# 4. P-SRAM Evaluation Kit

The Avalanche P-SRAM<sup>™</sup> parallel x32 evaluation kit enables the users to evaluate Avalanche's 3<sup>rd</sup> generation P-SRAM parallel x32 product using a Lattice LCMXO3LF-6900C FPGA connected to Avalanche daughter board via Avalanche proprietary FPGA based Asynchronous SRAM interface. The Lattice LCMXO3LF-6900C FPGA board communicates with the computer using a micro-USB cables type B connector.

The Lattice Mach XO3 evaluation board is a low-cost and easy-to-use development kit used to evaluate and quickly start a development with Avalanche AS3xxGB32 devices. Key features include:

- Small form factor, low cost

- Instant-on boot-up

- Flexible programing I/O expansion up to 384 I/O pins

- 4 expansion header landings to allow access to user GPIOs

- Supports both 1.8V and 3V I/Os

- Internal oscillator & PLLs

- Custom hardware timing

- Extended temperature flexibility

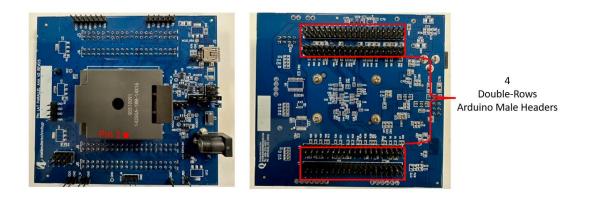

### Figure 8: Avalanche P-SRAM Daughter Board (front and back) with 142-Ball FBGA Socket

Figure 9: Lattice LCMX03L/LF-6900C FPGA board (back side) with 4 Installed Double-Row Arduino Female Header

Refer to the Eval Kit User Guide for more information on how to use the evaluation kit. Click <u>here</u> to download the user guide.

# 5. Revision History

| Revision | Date       | Change Summary                                                     |  |

|----------|------------|--------------------------------------------------------------------|--|

| REV A    | 10/25/2021 | Initial release                                                    |  |

| REV B    | 01/24/2023 | Updated Signal Description Table                                   |  |

|          |            | Updated Power-Up and Power Down Behavior Diagrams and Descriptions |  |

|          |            | Updated Avalanche Daughter Board Photo                             |  |