## **Table of Contents**

- Quick Intro to Avalanche

- USG Heritage

- High-Rel MRAM Differentiator

- Quality/Reliability

- Radiation Results

- Qualification and Ecosystem Update

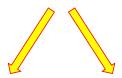

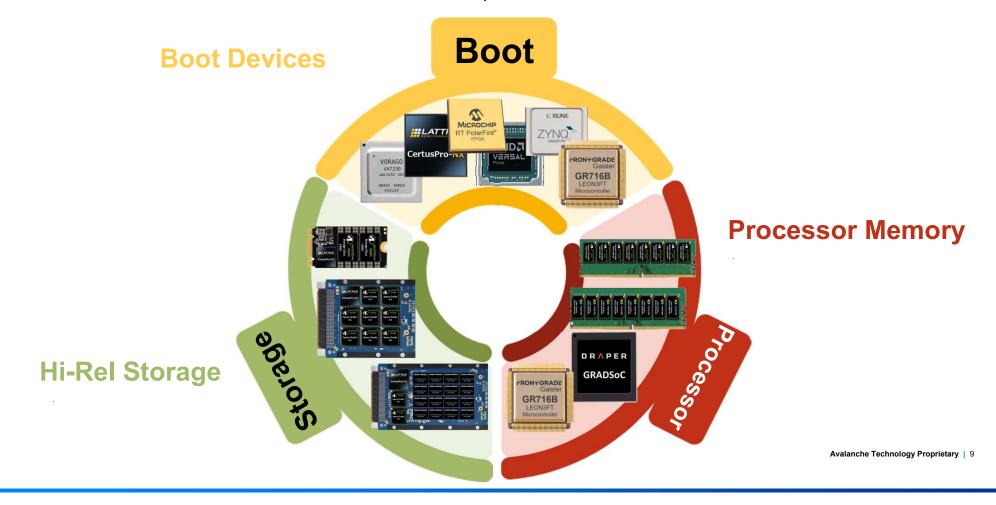

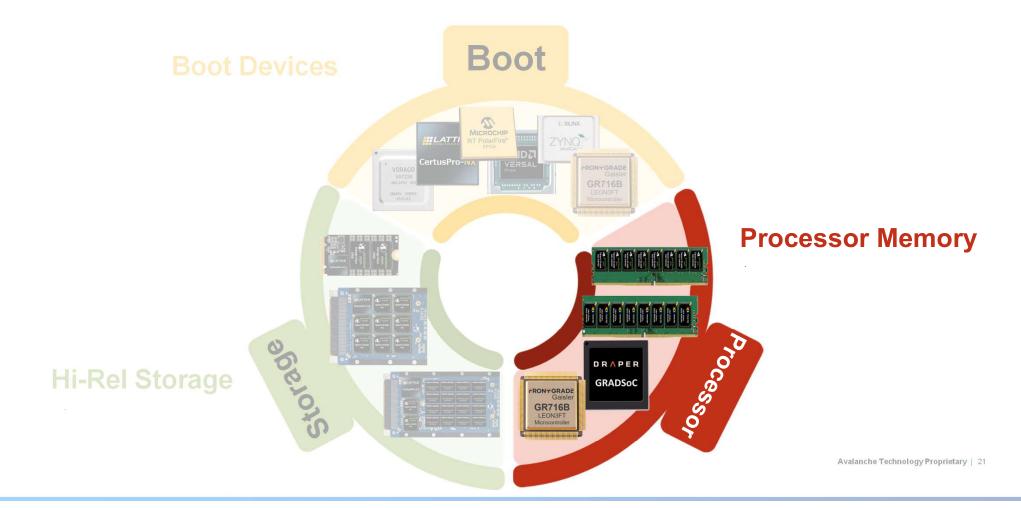

- Enabled Platforms Booting

- Enabled Platforms Storage Update

- Enabled Platforms Processing Memory Update

- Support and Resources

## **Avalanche Company Overview**

#### Hi-Rel STT pMTJ MRAM since 2006

## 19+ years STT MRAM Experience

## **Domestic Technology**

325 **Granted Patents** & counting

Most Next-Gen/STT MRAM Patents Stateside

#### Focused on Space and Hi-Rel Industrial

#### Hi-Rel Industrial Heritage Shipping volume to Industrial customers since 2019

Hi-Rel Focused

## **Growing Ecosystem**

Growing Fab and Partner Ecosystem...

#### Avalanche's DARPA connection

Dr. Yiming Huai – CTO/VP of Technology

- Yiming was a co-founder, board member, CTO and VP of Engineering of Grandis, Inc, a pioneer in Spin Transfer Torque MRAM (STT-MRAM). Founded in 2001.

- Huai successfully raised more than \$30M in private and government funding to develop STT MRAM.

- Yiming has come full circle since the \$14.7M in government funding from a DARPA program led by Dr. Dev Shenoy as Program Manager in 2008.

- Yiming came to Avalanche to achieve the goal of building a highly reliable dual use (industrial & space) MRAMs.

All Avalanche Executive are Semiconductor Industry Veterans – see more at: (https://www.avalanche-technology.com/company/leadership/)

#### **Avalanche High-Rel MRAM Differentiator for Space & Missiles**

Production Proven Products Today built on world class 22nm bulk CMOS process Avalanche's MRAM solutions deliver all these attributes in one product line

**Endurance**

Endure 10<sup>16</sup> write cycles / Unlimited read cycles ensuring consistent performance

**Performance**

Faster read and write speeds with low latency compared to traditional memory; scalable without a proportional increase in complexity

Radiation

Bulk CMOS with radiation tolerant techniques. TID >300kRad and SEE performance of ~75MeV cm<sup>2</sup>/mg

Reliability

Engineered and tested for harsh conditions like space with exposure to high levels of radiation and extreme temperatures. Built-in multi-bit ECC correction.

**Efficiency**

Consumes significantly less power compared to traditional memory both in standby mode and read / write operations

## With Volumes Comes Reliability (as of July 2025)

# Total MRAM Devices Shipped = 1,690,829 Total MRAM Terabits Shipped = 40.16 Tbits

Industrial Devices = 1,676,461

Industrial Terabits = 16.994 Tbits

Space Grade Devices = 14,368

Space Grade Terabits = **23.165 Tbits**

To put that in perspective:

it takes **379,534** x 64Mb Legacy MRAMs to store 23.165 Tbits

## MRAM Radiation Summary<sup>1</sup>

# **SEL Immune<sup>2</sup>:**

- 44 LET; Tested at 3.6V, 105°C & 125°C

- 62 LET; Tested at 3.0V, 105°C & 125°C

- 83 LET; Tested at 2.7V, 105°C & 125°C

## **SEFI/SEU Immune:**

- 83 LET; Tested at 2.5V, Room Temp

- Dynamic testing (Write/Read/Compare loop)

# New design guide coming - Recommendations for design community

<sup>1 -</sup> Testing performed by Frontgrade on Parallel MRAM Device

<sup>&</sup>lt;sup>2</sup> – 4 parts statically tested, 1 part dynamically tested

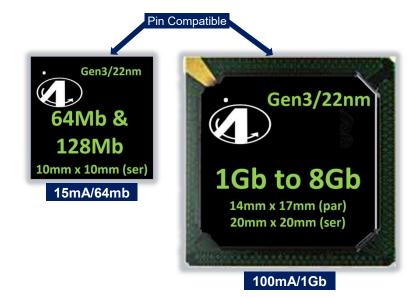

# **Product Qual Levels for Gen 3 – Scalability by Mission Requirement**

- Scalable Densities & Qual/Screening levels from Earth to Mars!

- Customers have many pin-compatible (by package) upscreened options through Falcon, Frontgrade and Micross

| Qual            | Package | Temp           | <b>Let</b><br>(MeV-cm²/mg) | TID<br>(Krad) | Burn In | Qual Syandards |

|-----------------|---------|----------------|----------------------------|---------------|---------|----------------|

| Space Grade     | Plastic | -40°C to 125°C | <= 55                      | 75*           | 48 Hrs  | JESD47H.01     |

| Space Grade-E   | Plastic | -40°C to 125°C | <= 75                      | 100*          | 168 Hrs | JESD47H.01     |

| PEMS I, II, III | Plastic | -40°C to 125°C | <= 75                      | 100-300*      | Custom  | NASA-INST-0001 |

| QML             | Ceramic | -55°C to 125°C | 75+                        | 300*          | Custom  | QML-M to V     |

<sup>\*</sup> Radiation performance tested durng Qualifaction and Characterization phase.

<sup>\*\*</sup> Radiation/Qual reports for an indivdual lot are available through datapacks on quals above JESD47H.01

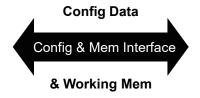

# **Aerospace Solutions – Enabling the Orbital Internet**

De-risking each space mission – Avalanche offers the only reliable, scalable and low power memory solutions for satellites, rocket missions and data centers in space

# **Highly Reliable Booting**

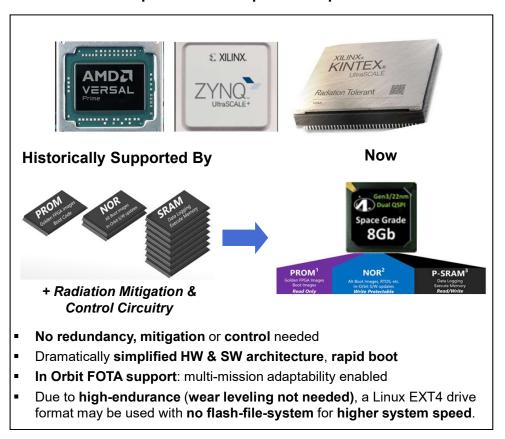

## AMD Xilinx | Enabled Booting and nvStorage for Devices

#### Software defined platforms for Space - respond to threats in real time

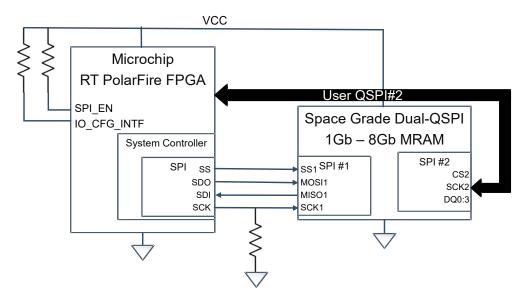

# Microchip | Enabled Auto-Updating RT PolarFire's Flash

#### **Auto-Updating RT PolarFire FPGAs with MRAM**

- RT PolarFire use SFDP (Serial Flash) Discoverable Parameters) – part of the JESD216 standard

- Avalanche DQSPI MRAMs do not support SFDP

- However, Avalanche DQSPI MRAMs have successfully auto-updated the RT PolarFire's on-board flash using its extended address register

# **Vorago | Reliable Booting for ARM-M4 Family of SoCs**

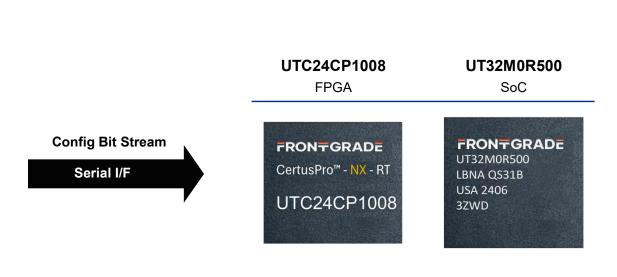

# Frontgrade/Lattice | Enabling Booting for FPGAs/SoCs

## Frontgrade | Enabling Booting & Working Memory for Gaisler **GR716 LEON3FT Processor**

# **Highly Reliable Storage**

## **Storage Solutions for Space**

Avalanche provides reference design with low level drivers

Partnership with ( EIDETICOM enabled plug and play NVMe stack

# **Storage Solutions for Space and Military**

Scanning satellites in LEO need data buffers.

# **VNX-Plus Data Buffer for LEO Satellites (8GB MRAM)**

## **Storage Solutions for Space and Military**

Communication Satellites in MEO need Hybrid drives

## 3U VPX Hybrid Data Storage (32Gb MRAM/1TB NAND)

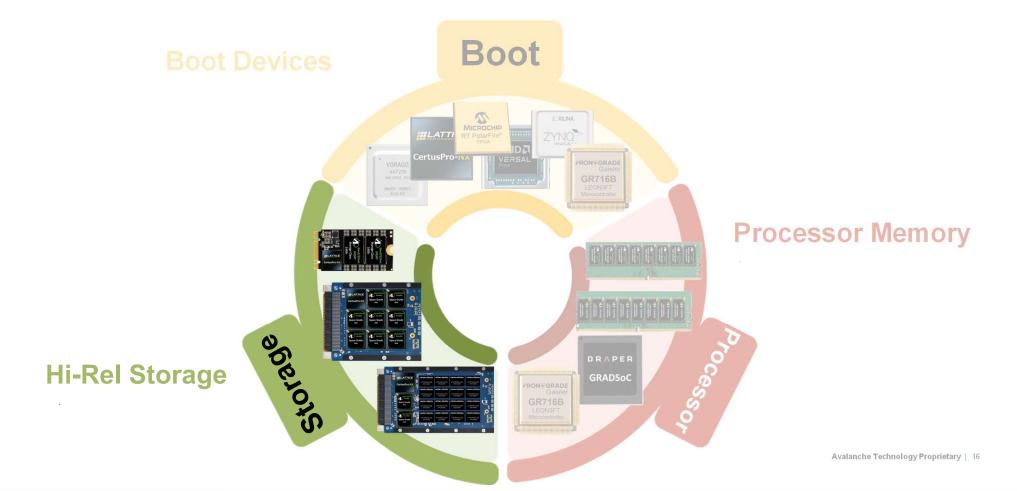

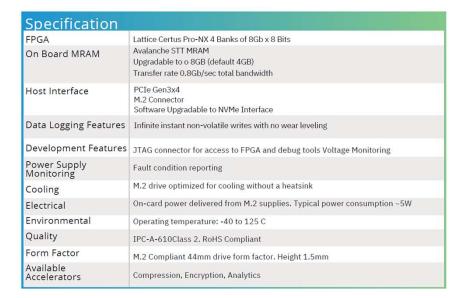

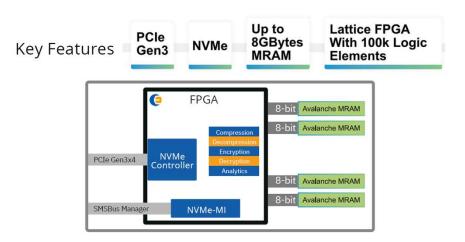

## **Storage Solutions for Hi-Rel Avionics**

- High Density (up to 4GB today)

- Highest Endurance (10<sup>16</sup> write cycles)

- High Reliability (Embedded ECC)

- Soft Error Immune

- Standard PCle Gen 3 Interface

- Multiple Channels

- Low Latency

- · No Wear Leveling Required

# **Highly Reliable Processor Memory**

Avalanche Technology Proprietary | 22

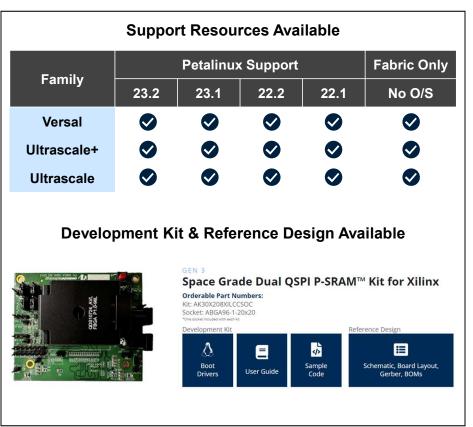

# Support Resources @ www.avalanche-technology.com

#### Datasheets, models, reference designs

Boot module: Petalinux drivers, User Guide (Versal boot)

Gen 3 reference designs

IBIS & Verilog models

#### **Radiation test reports**

Gen 2 test report accessed via website (NASA)

Gen 3 reports available by request

#### **Visionary White Papers**

Innovation enabled by Avalanche Data Centers in Space...

...why the key to satellite scalability and resilience

NEW: Al Computing in Space

#### **Newsletters**

Quarterly, register on main page

#### **Brochures**

Overall MRAM tech for hi-rel apps Space Grade products

#### **Space-centric Blogs**

Datacenter in Space series Why our MRAM is ideal for space

#### Gen 3 Dev Kit Options for DQSPI – 64Mb to 8Gb

#### High Density DQSPI (1Gb to 8Gb) – 96-ball (20x20mm)

#### Dual QSPI P-SRAM™ Dev Kit

- Complete eval kit uses Lattice MACHX03 FPGA board connected to Avalanche MRAM daughterboard via standard QSPI I/F & Arduino connector.

- Host control w/ embedded ARM via micro-USB port.

- Part number: AK30x208LATCCSOC

For evaluation & prototyping of h/w to interface with our high-density devices to most FPGAs & SoCs, minus those that use VCK190 like Versal. Optimized for multiple mission images.

#### **Dual QSPI P-SRAM™ Plug In Card for** Xilinx VCK19X Board

- Plug-in card for existing Xilinx/AMD VCK19X dev kits.

- Supports rapid booting of Xilinx/AMD Versal & UltraScale+

- Connects via Samtec connector

- Part number: AK30x208XILCCSOC

For evaluation & prototyping of hw to those that use VCK190 like Versal

#### Low Density DQSPI (64Mb & 128Mb) - 56-ball (10x10mm)

- Complete eval kit uses Lattice LCMXO3L/LF-6900C FPGA board connected to Avalanche socketed daughterboard via proprietary Asynchronous SRAM I/F.

- · Host control w/ embedded ARM via micro-USB port.

- Part number: AK30X208LATCTSOE

For evaluation & prototyping of h/w to interface with our low-density devices to FPGAs & SoCs with compact mission image requirements.

## **Advanced Boot Solutions Enabling SW-Defined Platforms**

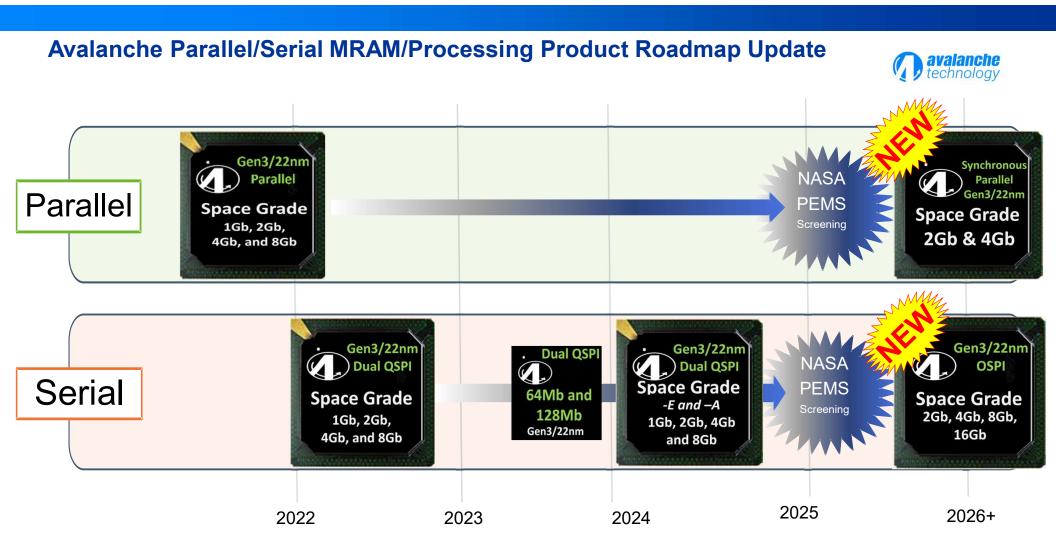

Avalanche Technology Announces Support for NASA PEMS Qualifica and Screening

In response to unprecedented demand for extended qualification & screening flows, Avalanche rolls out pin compatible NASA PEMS options for enabling Dual QSPI MRAM family.

FREMONT, CA, April 8, 2024 — Avalanche Technology, the leader in next generation MRAM technology, announced today the launch of a new product derivative to address the growing demand from the aerospace and defense community for extended qualification and screening solutions, particularly NASA

Leveraging Avalanche's Gen 3 Space Grade MRAM products being broadly adopted by the defense industrial base and commercial space customers, the new pin compatible PEMS qualified and screened versions of the popular Dual QSPI MRAMs will roll out mid-year.

alanche Technology Selected to Support Mercury's First Space-Qu Processing Board Using AMD's Xilinx Versal Al Core

Mercury is leveraging Avalanche's PSRAM(TM) products to build the next family of SWaP optimize orbit software-defined processing platforms

FREMONT, Calif., Nov. 8, 2023 /PRNewswire-PRWeb/ — Avalanche Technology, the leader in next generation MRAM technology, announced today that its Persistent-SRAM (P-SRAM) products were by Mercury Systems for the new SCFE6933, a next-generation processor board that will enable fa processing of data in orbit. The high-density 8Gb DQSPI Space Grade Persistent SRAM with further scalability is the ideal companion to the AMD (Xilinx) Versal Adaptive SoC platform that is feature platform.