Radiation Tolerant and Radiation Hardened FPGAs and Microcontrollers are often used in aerospace applications. More recently, owing to the increased resolution of available sensors, space applications must perform rapidly increasing amounts of on-board processing as sensor resolution is increasing faster than downlink bandwidth. FPGA vendors have raced to qualify FPGAs for these signal processing applications. These FPGAs require configuration memory (usually NOR Flash) and are often paired with expansion memories (usually SRAM or DRAM) and/or data logging memories (usually battery backed SRAM or MRAM used in conjunction with non-volatile storage class memory). This post focusses on the memories used in space applications.

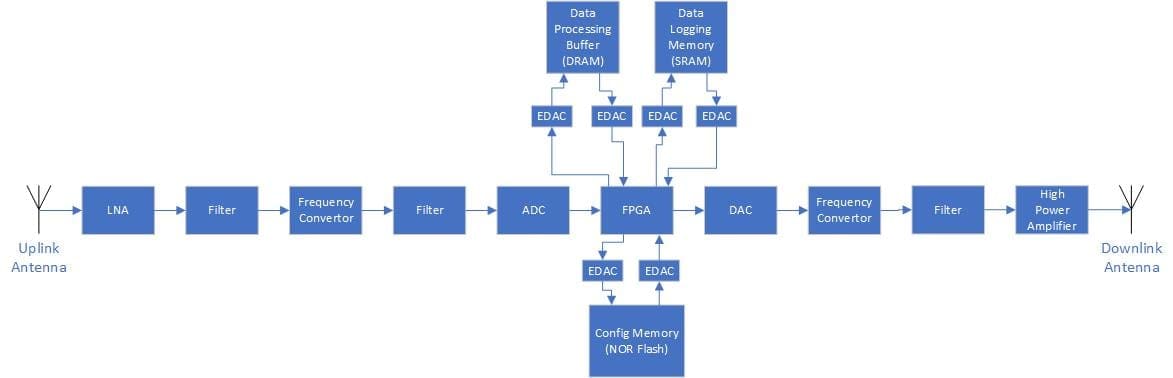

Fig 1. Block Diagram of a High Throughput Telecommunications Satellite Payload

The above block diagram shows a high throughput telecommunications system. The system has a core processing subsystem comprising of an FPGA, a configuration memory (Q-SPI NOR Flash) to configure the FPGA, a DDRx DRAM which is used as a processing buffer and a datalogging memory. The inadequate radiation hardness of these memories is usually addressed by adding EDACs. In general, EDAC schemes contain a Hamming code encoder and a Hamming code decoder, which are used to add or remove redundant bits of data for error detection and correction. In such an implementation, the controller (FPGA or MCU) implements EDAC encoder and decoder and all memory accesses go through these blocks. However, EDAC by themselves do not solve the problem completely. To prevent accumulation of errors, the memory contents need to be scrubbed periodically. As one can imagine, resulting implementations impose cost, performance, and design-complexity related challenges.

MRAM technology is analogous to Flash technology for its non-volatility but with SRAM compatible read/write timings. MRAM is a true random-access memory; allowing both reads and writes to occur randomly in memory. MRAM isideal for applications that must store and retrieve data without incurring large latency penalties. It offers low latency, low power, virtually infinite endurance and retention, and scalable non-volatile memory technology. Additionally, Avalanche’s high reliability MRAM are designed using Spin Transfer Torque MRAM (STT-MRAM) technology which is scalable to higher densities. This technology makes it possible to provide DDR3 DRAM and NOR Flash replacement products – a high-reliability, high-density Persistent DRAM (P-DRAM) with a high-performance DDR3 interface and a high-reliability, high-density Serial P-SRAM with a Q-SPI interface.

In contrast to SRAMs, DRAMs and Flash, MRAMs are immune to radiation effects. Consequently, they do not need EDAC circuitry implementation in the controller. Recent NASA testing has found Avalanche’s Space Grade STT-MRAM devices to have excellent immunity to radiation. No notable changes were observed to the electrical parameters tested up to at least 1 Mrad(Si) of Total Ionizing Dose. Similarly, Single Events Effects testing, also conducted by NASA, found SEL LETth> 85.4, SEFI LETth>120.7, 1.3< SEFI LETth<1.84 and SEFI σ 3.2×10-8 cm2. It should also be noted that the NASA test report concluded “no parts were permanently damaged or degraded during heavy-ion testing.”

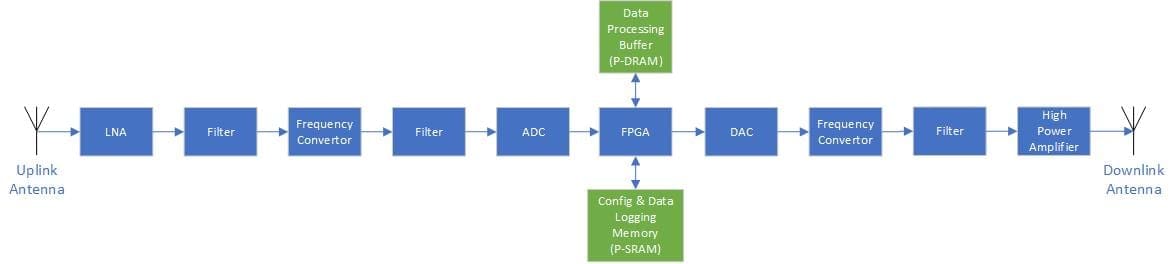

The next generation space grade devices from Avalanche have been designed from ground up with reliability in space as the key objective. Even though the memory array is virtually immune to radiation effects, these devices include multi-bit ECC circuitry which further improves reliability. Additionally, all the on-chip latches and registers have TMR followed by a voter circuit to provide robust performance in space. Last but not the least, in the unlikely event that the device encounters an unrecoverable error, the on-chip EDAC circuitry generates an interrupt which can be used by the controller to reset the control circuitry in the memory. When used in space applications like the above described telecommunications satellite, circuit design is simplified (see figure 2 below) yielding cost and complexity reduction.

Fig 2. Block Diagram of a High Throughput Telecommunications Satellite Payload using Avalanche Technology’s P-DRAM and P-SRAM

Avalanche Technology’s high reliability MRAM devices are ideal for non-volatile memory applications in Aerospace products (automation, engine control, security system, navigation, system log and black box). Learn more about currently available products, access test reports quoted in this blog post, or sign up for the early access program for forthcoming MRAM products HERE.